Marktbericht über die Mikroelektronikverpackung mit gestapelten Chips 2025: Wachstum, Technologiewechsel und strategische Einblicke für die nächsten 5 Jahre. Erkunden Sie wichtige Trends, Prognosen und wettbewerbliche Dynamiken, die die Branche prägen.

- Zusammenfassung & Marktübersicht

- Wichtige Technologietrends in der Mikroelektronikverpackung mit gestapelten Chips

- Wettbewerbslandschaft und führende Akteure

- Marktwachstumsprognosen (2025–2030): CAGR, Umsatz- und Volumenanalyse

- Regionale Marktanalyse: Nordamerika, Europa, Asien-Pazifik und Rest der Welt

- Zukünftige Ausblicke: Neueste Anwendungen und Investitionsschwerpunkte

- Herausforderungen, Risiken und strategische Chancen

- Quellen & Referenzen

Zusammenfassung & Marktübersicht

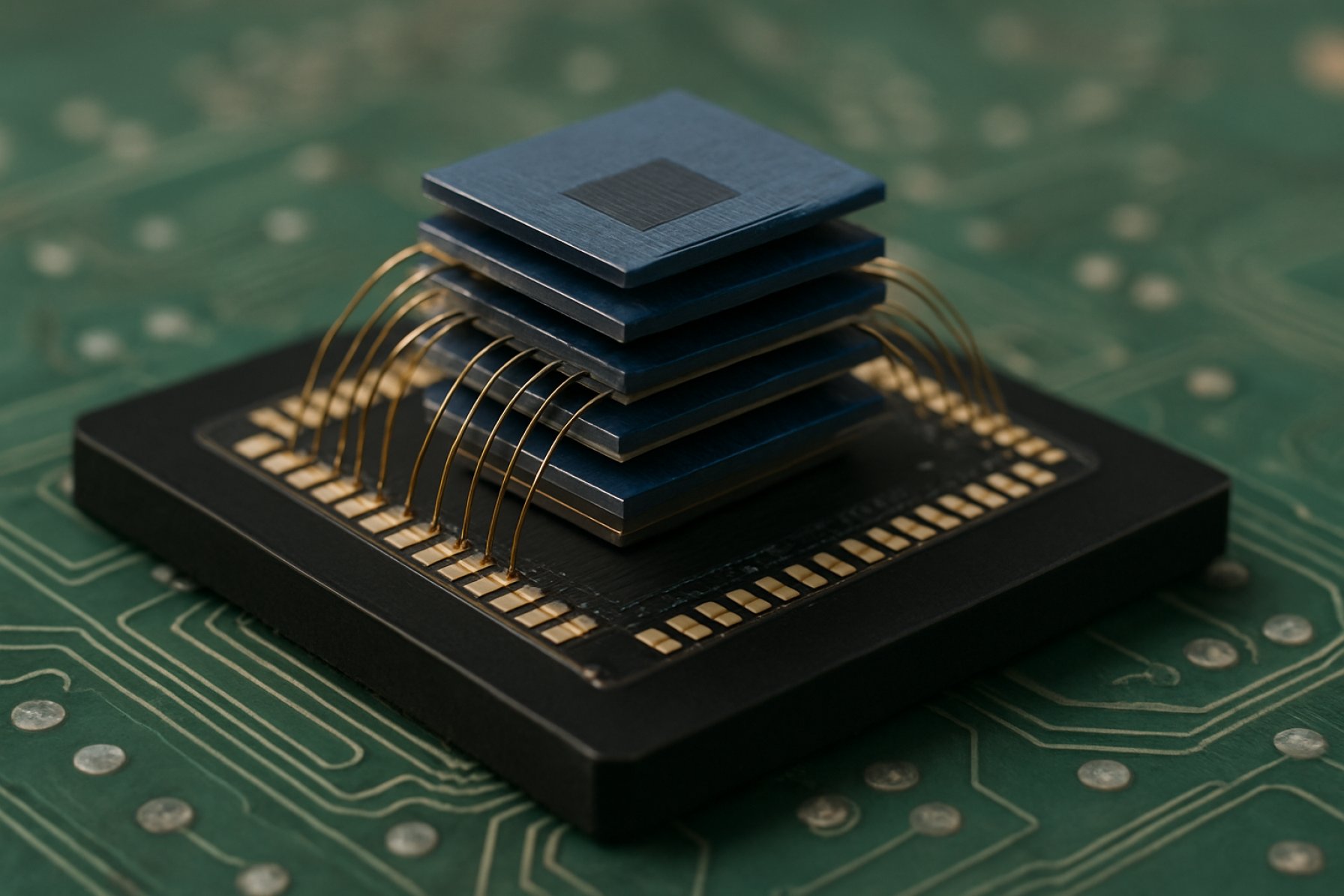

Die Mikroelektronikverpackung mit gestapelten Chips bezieht sich auf die Integration mehrerer Halbleiterchips in einem einzigen Gehäuse, die vertikal angeordnet sind, um Raum, Leistung und Funktionalität zu optimieren. Diese fortschrittliche Verpackungstechnologie ist entscheidend, um die steigenden Anforderungen an Miniaturisierung, höhere Leistung und Energieeffizienz in Bereichen wie Verbraucher elektronischen Geräten, Automobilindustrie, Telekommunikation und Rechenzentren zu erfüllen. Im Jahr 2025 verzeichnet der globale Markt für Mikroelektronikverpackungen mit gestapelten Chips ein starkes Wachstum, das durch die Verbreitung von 5G-Geräten, Anwendungen der künstlichen Intelligenz (KI) und des Internet der Dinge (IoT) vorangetrieben wird.

Laut Gartner wird prognostiziert, dass der Markt für Verpackungen mit gestapelten Chips in den Jahren 2023 bis 2027 eine jährliche Wachstumsrate (CAGR) von über 8% erreichen wird, wobei die Einnahmen bis 2025 voraussichtlich 12 Milliarden US-Dollar übersteigen werden. Dieses Wachstum wird durch die zunehmende Einführung von 3D-Integrationsschaltungen (3D-ICs), System-in-Package (SiP)-Lösungen und Hochbandbreitenspeichermodulen (HBM) unterstützt, die alle gestapelte Chiparchitekturen nutzen, um die Leistung zu verbessern und die Baugröße zu reduzieren.

Wichtige Akteure der Branche wie TSMC, Samsung Electronics und Intel Corporation investieren erheblich in Forschung und Entwicklung, um die Technologien der Durchführungen durch Silizium (TSV) und der Wafer-Level-Verpackung (WLP) voranzutreiben. Diese Innovationen ermöglichen höhere Anschlussdichten, verbesserte Wärmeableitung und einen geringeren Stromverbrauch, die für Anwendungen der nächsten Generation in KI-Beschleunigern, fortschrittlichen Fahrerassistenzsystemen (ADAS) und Hochleistungsrechnern (HPC) entscheidend sind.

Regional dominiert Asien-Pazifik den Markt für Verpackungen mit gestapelten Chips und macht mehr als 60% der globalen Produktionskapazität aus, was im Wesentlichen der Präsenz führender Foundries und OSAT (Outsourced Semiconductor Assembly and Test)-Anbieter in Ländern wie Taiwan, Südkorea und China zu verdanken ist. Auch Nordamerika und Europa verzeichnen eine zunehmende Akzeptanz, insbesondere im Bereich der Automobelelektronik und der Rechenzentrumsinfrastruktur, wie von IC Insights festgestellt.

Zusammenfassend ist die Mikroelektronikverpackung mit gestapelten Chips eine Schlüsseltechnologie für die Entwicklung der Halbleiterindustrie im Jahr 2025, die eine höhere Integration, Leistung und Effizienz über ein breites Anwendungsspektrum ermöglicht. Der Kurs des Marktes wird durch fortwährende technologische Fortschritte, strategische Investitionen führender Akteure und die stetige Nachfrage nach intelligenteren, kleineren und leistungsstärkeren elektronischen Systemen geprägt.

Wichtige Technologietrends in der Mikroelektronikverpackung mit gestapelten Chips

Die Mikroelektronikverpackung mit gestapelten Chips steht an der Spitze der Halbleiterinnovation und ermöglicht eine höhere Geräteleistung, erweiterte Funktionalität und reduzierte Baugrößen durch die vertikale Integration mehrerer Halbleiterchips in einem einzigen Gehäuse. Während sich die Industrie auf das Jahr 2025 zubewegt, prägen mehrere wichtige Technologietrends die Entwicklung und Akzeptanz von Verpackungslösungen mit gestapelten Chips.

- Fortschrittliche Durchführungen durch Silizium (TSV): TSV-Technologie bleibt ein grundlegendes Element für Hochdichte-Chipstapelung und bietet latenzarme, hochbandbreitige Verbindungen zwischen vertikal ausgerichteten Chips. Im Jahr 2025 verfeinern Hersteller die TSV-Prozesse, um den Durchmesser und den Abstand der Durchführungen zu verringern, wodurch die Anschlussdichte erhöht und die elektrische Leistung verbessert wird. Dies ist besonders kritisch für Hochleistungsrechner (HPC) und Anwendungen der künstlichen Intelligenz (KI), bei denen die Speicherdurchsatz ein Engpass darstellt. TSMC und Samsung Electronics sind führend bei der Kommerzialisierung fortschrittlicher TSV-basierter 2.5D- und 3D-IC-Verpackungen.

- Hybride Bonding-Techniken: Hybrides Bonding, das direkte Kupfer-zu-Kupfer- und Dielektrikum-zu-Dielektrikum-Bonding kombiniert, gewinnt als Methode zur Erreichung ultra-feiner Pitch-Verbindungen und verbesserter elektrischer Eigenschaften an Bedeutung. Diese Technologie ermöglicht das Stapeln mit weniger als 10 Mikrometer Pitch, was für die nächste Generation der Logik-Speicher-Integration unerlässlich ist. Amkor Technology und Intel Corporation haben erhebliche Investitionen in hybrides Bonding sowohl für Speicher- als auch Logikgeräte angekündigt.

- Heterogene Integration: Der Trend zur Integration unterschiedlicher Chiplets – wie Logik, Speicher, RF und Analog – in einem einzigen gestapelten Gehäuse beschleunigt sich. Dieser Ansatz ermöglicht optimierte Prozessknoten für jede Funktion, wodurch die Gesamtleistung und Energieeffizienz des Systems verbessert werden. Der Branchenverband SEMI hebt die heterogene Integration als Schlüsseltechnologie für fortschrittliche Automobil-, 5G- und Edge-Computing-Lösungen hervor.

- Innovationen im Wärme-Management: Mit der Erhöhung der Leistungsdichte durch das Chip-Stapeln werden fortschrittliche thermische Schnittstellenmaterialien (TIMs), Mikrofluidkühlung und integrierte Wärmeverstreuer entwickelt, um die Wärmeableitung zu managen. Die Yole Group berichtet, dass effektives Wärme-Management inzwischen ein primäres Unterscheidungsmerkmal im Design von gestapelten Chip-Paketen ist, insbesondere für Märkte im Bereich Rechenzentren und KI-Beschleuniger.

- Automatisierte Tests und Inspektion: Die Komplexität von gestapelten Chip-Baugruppen erfordert fortschrittliche Test- und Inspektionslösungen, einschließlich hochauflösender Röntgen- und KI-gesteuerter Fehlererkennung. KLA Corporation und Teradyne erweitern ihr Angebot, um den einzigartigen Herausforderungen der Zuverlässigkeit und Ausbeute bei Multi-Chip-Paketen gerecht zu werden.

Diese Technologietrends treiben den Markt für Mikroelektronikverpackungen mit gestapelten Chips insgesamt in Richtung größerer Integration, Leistung und Zuverlässigkeit, und positionieren ihn als kritischen Faktor für die nächsten Generationen elektronischer Systeme in 2025 und darüber hinaus.

Wettbewerbslandschaft und führende Akteure

Die Wettbewerbslandschaft des Marktes für Mikroelektronikverpackungen mit gestapelten Chips im Jahr 2025 ist geprägt von intensiver Innovation, strategischen Partnerschaften und einem Fokus auf fortschrittliche Herstellungsfähigkeiten. Dieser Sektor wird durch die Nachfrage nach höherer Geräteleistung, Miniaturisierung und Integration in Anwendungen wie Smartphones, Hochleistungsrechner, Automobelelektronik und IoT-Geräte angetrieben. Die wichtigsten Akteure nutzen ihr Fachwissen bei der Wafer-Level-Verpackung, der TSV-Technologie und der heterogenen Integration, um einen Wettbewerbsvorteil zu wahren.

Die Marktführer sind etablierte Anbieter von Halbleiterverpackungen und Montageservices, darunter Amkor Technology, ASE Technology Holding und TSMC. Diese Unternehmen haben beträchtliche Investitionen in Forschung und Entwicklung sowie Produktionskapazitäten getätigt, um die hochvolumige Fertigung von gestapelten Chiplösungen zu unterstützen. So werden die fortschrittlichen CoWoS (Chip-on-Wafer-on-Substrate)- und SoIC (System on Integrated Chips)-Technologien von TSMC häufig für hochwertige Computing- und KI-Anwendungen eingesetzt, während Amkor Technology und ASE Technology Holding ein breites Portfolio an 2.5D- und 3D-Verpackungsdiensten für Verbraucher- und Unternehmensmärkte anbieten.

IDMs (Integrated Device Manufacturers) wie Intel Corporation und Samsung Electronics sind ebenfalls prominent, indem sie die Verpackung gestapelter Chips in ihre Produktroadmaps integrieren, um die Leistungsfähigkeit der Chips und die Energieeffizienz zu verbessern. Intels Foveros-Technologie und Samsungs X-Cube-Plattform sind Beispiele für proprietäre Ansätze zur vertikalen Integration und chipletbasierter Architekturen.

Aufstrebende Akteure und Nischenanbieter, darunter JCET Group und Powertech Technology Inc., gewinnen an Bedeutung, indem sie maßgeschneiderte Lösungen anbieten und spezifische Vertikale wie Automobil- und industrielle Elektronik ansprechen. Diese Unternehmen arbeiten häufig mit fabless Halbleiterfirmen und Systemintegratoren zusammen, um maßgeschneiderte gestapelte Chip-Pakete zu liefern.

Die Wettbewerbsumgebung wird zudem durch anhaltende M&A-Aktivitäten, Technologielizenzierung und Joint Ventures geprägt, da Unternehmen ihre Fähigkeiten und ihre globale Reichweite erweitern möchten. Laut Yole Group wird erwartet, dass der Markt weiterhin Konsolidierungen erleben wird, wobei führende Akteure in nächste Generationen von Verbindungen, fortschrittliche Materialien und Automatisierung investieren, um den sich entwickelnden Bedürfnissen der Märkte für KI, 5G und Edge Computing gerecht zu werden.

Marktwachstumsprognosen (2025–2030): CAGR, Umsatz- und Volumenanalyse

Der Markt für Mikroelektronikverpackungen mit gestapelten Chips ist zwischen 2025 und 2030 auf eine robuste Wachstumsdynamik eingestellt, die durch die steigende Nachfrage nach leistungsstarken, miniaturisierten elektronischen Geräten in den Bereichen Verbraucher elektronischer Geräte, Automobil und Rechenzentrum getrieben wird. Laut Prognosen von MarketsandMarkets wird der globale Markt für 3D-IC- und gestapelte Chipverpackungen voraussichtlich eine jährliche Wachstumsrate (CAGR) von etwa 12% während dieses Zeitraums verzeichnen. Dieser Wachstumskurs wird durch die zunehmend verbreitete Annahme fortschrittlicher Verpackungslösungen unterstützt, um die Einschränkungen traditioneller 2D-Architekturen, insbesondere in Bezug auf Energieeffizienz, Baugröße und Bandbreite, anzugehen.

Die Umsatzprognosen deuten darauf hin, dass das Segment der Mikroelektronikverpackungen mit gestapelten Chips bis 2030 die 15 Milliarden USD übersteigen wird, gegenüber geschätzten 8,5 Milliarden USD im Jahr 2025. Dieser Anstieg wird auf das Wachstum von Anwendungen der künstlichen Intelligenz (KI), der 5G-Infrastruktur und des Edge Computing zurückgeführt, die alle eine höhere Anschlussdichte und ein verbessertes Wärme-Management erfordern – entscheidende Vorteile, die von gestapelten Chiparchitekturen angeboten werden. Gartner hebt hervor, dass der Übergang der Halbleiterindustrie zur heterogenen Integration und System-in-Package (SiP)-Lösungen die Akzeptanz von Technologien für gestapelte Chips weiter beschleunigen wird.

In Bezug auf das Volumen wird projiziert, dass die Anzahl der ausgelieferten Einheiten von gestapelten Chips von 2025 bis 2030 mit einer jährlichen Wachstumsrate von 13–14% steigen wird, was sowohl eine erhöhte Durchdringung in hochvolumigen Verbrauchergeräten als auch einen wachsenden Einsatz in der Automobelelektronik und im industriellen IoT widerspiegelt. Die Yole Group berichtet, dass führende Foundries und OSATs (Outsourced Semiconductor Assembly and Test-Anbieter) ihre Investitionen in fortschrittliche Verpackungslinien hochfahren, um diese erwartete Nachfrage zu decken, wobei Asien-Pazifik aufgrund seines etablierten Halbleiterfertigungsecosystems das dominierende Produktionszentrum bleibt.

- CAGR (2025–2030): 12–14%

- Umsatz (2030): Über 15 Milliarden USD

- Volumewachstum: Getrieben durch Verbraucher elektronischer Geräte, Automobil und Rechenzentrum

- Schlüsselregionen: Asien-Pazifik führt, gefolgt von Nordamerika und Europa

Insgesamt steht der Markt für Mikroelektronikverpackungen mit gestapelten Chips vor einer signifikanten Expansion, die durch technologische Innovationen und den unaufhörlichen Drang nach höherer Leistung und Integration in nächste Generationen elektronischer Systeme angetrieben wird.

Regionale Marktanalyse: Nordamerika, Europa, Asien-Pazifik und Rest der Welt

Der globale Markt für Mikroelektronikverpackungen mit gestapelten Chips erfährt ein dynamisches Wachstum, wobei die regionalen Trends durch technologische Innovationen, die Nachfrage der Endverbraucher und Entwicklungen in der Lieferkette geprägt sind. Im Jahr 2025 weisen Nordamerika, Europa, Asien-Pazifik und der Rest der Welt (RoW) jeweils unterschiedliche Marktcharakteristika und Wachstumsfaktoren auf.

- Nordamerika: Der nordamerikanische Markt wird von robusten Investitionen in fortschrittliche Halbleiterfertigung und einer starken Präsenz führender Technologieunternehmen angetrieben. Die Region profitiert von erheblichen F&E-Aktivitäten, insbesondere in den Vereinigten Staaten, wo der Drang zur heimischen Chipproduktion durch staatliche Initiativen wie das CHIPS-Gesetz unterstützt wird. Wichtige Anwendungen umfassen Hochleistungsrechner, Automobelelektronik und Verteidigungssysteme. Laut der Semiconductor Industry Association wird Nordamerika voraussichtlich ein stetiges Wachstum im Bereich der Mikroelektronikverpackungen mit gestapelten Chips aufrechterhalten, angetrieben durch die Nachfrage nach miniaturisierten, hochdichten Lösungen in KI und 5G-Infrastruktur.

- Europa: Der europäische Markt ist geprägt von einem Fokus auf Automobil-, industrielle Automatisierungs- und IoT-Anwendungen. Der Schwerpunkt der Region auf Qualität und Zuverlässigkeit sowie strenge regulatorische Standards fördern die Einführung fortschrittlicher Verpackungstechnologien. Initiativen wie das europäische Chips-Gesetz zielen darauf ab, die lokalen Halbleiterfähigkeiten zu stärken. Laut SEMI investieren europäische Hersteller zunehmend in Lösungen mit gestapelten Chips, um die wachsenden Sektoren für Elektrofahrzeuge und intelligente Fertigung der Region zu unterstützen.

- Asien-Pazifik: Asien-Pazifik dominiert den globalen Markt für Mikroelektronikverpackungen mit gestapelten Chips und hält 2025 den größten Marktanteil. Diese Führungsposition wird durch die Präsenz großer Foundries und OSAT (Outsourced Semiconductor Assembly and Test)-Anbieter in Ländern wie Taiwan, Südkorea, China und Japan untermauert. Die rasche Akzeptanz von Verbraucher elektronischen Geräten, Smartphones und Rechenzentren in der Region steigert die Nachfrage nach hochdichter Verpackung. Laut IC Insights wird das Marktwachstum in Asien-Pazifik weiter durch staatliche Anreize und aggressive Kapazitätserweiterungen führender Akteure beschleunigt.

- Rest der Welt (RoW): Der RoW-Segment, einschließlich Lateinamerika, dem Nahen Osten und Afrika, bleibt noch im Anfangsstadium, zeigt jedoch Wachstumspotenzial, da digitale Transformationsinitiativen zunehmen. Investitionen in Telekommunikationsinfrastrukturen und aufkommende Elektronikfertigungshubs werden voraussichtlich allmählich die Nachfrage nach Lösungen für die Mikroelektronikverpackung mit gestapelten Chips erhöhen, wie von Gartner angemerkt.

Insgesamt spiegeln sich die regionalen Dynamiken im Jahr 2025 in einer Konvergenz von Innovation, politischer Unterstützung und Nachfrage der Endmärkte wider, wobei Asien-Pazifik in Bezug auf Volumen führt und Nordamerika sowie Europa sich auf wertschöpfende, spezialisierte Anwendungen konzentrieren.

Zukünftige Ausblicke: Neueste Anwendungen und Investitionsschwerpunkte

Der Ausblick für die Mikroelektronikverpackung mit gestapelten Chips im Jahr 2025 wird durch rasante Fortschritte in der Halbleiterintegration, die Verbreitung von KI und Hochleistungsrechnern sowie die zunehmende Nachfrage nach miniaturisierten, hochdichten elektronischen Systemen geprägt. Die Verpackung mit gestapelten Chips, die die vertikale Integration mehrerer Halbleiterchips in einem einzigen Gehäuse umfasst, wird zunehmend als Schlüsseltechnologie für Geräte der nächsten Generation in mehreren wachstumsstarken Sektoren anerkannt.

Neueste Anwendungen sind insbesondere in Rechenzentren, 5G-Infrastrukturen und Edge-Computing präsent. Der Bedarf an höherer Bandbreite und niedrigerer Latenz in diesen Umgebungen treibt die Akzeptanz von 2.5D- und 3D-gestapelten Chiparchitekturen an, die verbesserte elektrische Eigenschaften und reduzierte Verbindungslängen bieten. Im Jahr 2025 wird erwartet, dass die Integration von Hochbandbreitenspeichermodulen (HBM) mit Logikchips beschleunigt wird, um den Rechenanforderungen von KI-Beschleunigern und fortschrittlichen Grafikprozessoren gerecht zu werden. Unternehmen wie Samsung Electronics und TSMC investieren erheblich in fortschrittliche Verpackungslinien, um dieser Nachfrage gerecht zu werden.

Eine weitere aufkommende Anwendung ist im Automobilsektor, wo die Mikroelektronikverpackung mit gestapelten Chips die Entwicklung kompakter, zuverlässiger Module für fortschrittliche Fahrerassistenzsysteme (ADAS) und autonome Fahrzeuge ermöglicht. Die strengen Anforderungen der Automobilindustrie an das Wärme-Management und die Zuverlässigkeit treiben Innovationen in den Technologien der Durchführungen durch Silizium (TSV) und der Wafer-Level-Verpackung voran, wobei Anbieter wie Infineon Technologies und NXP Semiconductors ihre Portfolios erweitern, um diesen Anforderungen gerecht zu werden.

Investitionsschwerpunkte im Jahr 2025 werden voraussichtlich auf Asien-Pazifik liegen, insbesondere auf Taiwan, Südkorea und China, wo staatliche Anreize und robuste Foundry-Ökosysteme die Forschung und Entwicklung sowie die Kapazitätserweiterung beschleunigen. Laut Gartner wird erwartet, dass der globale Markt für fortschrittliche Verpackungen bis 2025 mit einer CAGR von über 7% wächst, wobei gestapelte Chip-Lösungen einen signifikanten Anteil dieses Wachstums ausmachen. Risikokapital und strategische Investitionen fließen auch in Startups, die neuartige Verbindungsmaterialien und heterogene Integrationstechniken entwickeln, wie in den jüngsten Finanzierungsrunden hervorgehoben, die von CB Insights verfolgt werden.

- KI und HPC: Mikroelektronikverpackung für KI-Beschleuniger und GPUs

- Automobil: Hochzuverlässige, kompakte Module für ADAS und Elektrofahrzeuge

- 5G/Edge: Niedriglatenz- und hochbandbreitige Lösungen für Netzwerkinfrastrukturen

- Asien-Pazifik: Führende Region für Investitions- und Fertigungsexpansion

Zusammenfassend wird 2025 die Mikroelektronikverpackung mit gestapelten Chips im Mittelpunkt der Halbleiterinnovation stehen, mit starkem Momentum in den Bereichen KI, Automobil und Kommunikation sowie erheblichen Investitionstätigkeiten in Asien-Pazifik und bei Startups für fortschrittliche Materialien.

Herausforderungen, Risiken und strategische Chancen

Die Mikroelektronikverpackung mit gestapelten Chips, ein Eckpfeiler der fortschrittlichen Halbleiterintegration, sieht sich im Jahr 2025 einer komplexen Landschaft von Herausforderungen und Risiken gegenüber, bietet aber auch bedeutende strategische Chancen für Branchenakteure. Die Haupttechnische Herausforderung bleibt das Wärme-Management. Mit zunehmender vertikaler Integration von Chips wird die Wärmeableitung immer problematischer, was die Zuverlässigkeit und die Leistungsfähigkeit der Geräte gefährdet. Fortschrittliche thermische Schnittstellenmaterialien und innovative Wärmeverteilungskonzepte werden erforscht, aber ihre Integration erhöht die Kosten und die Komplexität des Herstellungsprozesses (SEMI).

Die Ausbeute- und Zuverlässigkeitsrisiken sind in Architekturen mit gestapelten Chips ebenfalls erhöht. Die höhere Anzahl von Verbindungen, wie zum Beispiel Durchführungen durch Silizium (TSVs), erhöht die Wahrscheinlichkeit von Defekten, die die Gesamtausbeute beeinflussen. Darüber hinaus bringt die heterogene Integration – die Kombination von Chips aus verschiedenen Fertigungsnoden oder Foundries – Kompatibilitäts- und Testherausforderungen mit sich. Der Bedarf an fortschrittlichen Inspektions- und Messtechnologien wächst, aber diese Lösungen können die Kapitalausgaben erheblich erhöhen (TechInsights).

Die Komplexität der Lieferkette ist ein weiteres kritisches Risiko. Die Mikroelektronikverpackung mit gestapelten Chips erfordert oft die Zusammenarbeit mehrerer Anbieter für Wafer, Substrate und Montageleistungen. Störungen in einem Segment können die Produktion verzögern und die Kosten erhöhen. Geopolitische Spannungen und Exportkontrollen, insbesondere im Technologietransfer zwischen den USA und China, verschärfen die Verwundbarkeiten der Lieferkette weiter (Gartner).

Trotz dieser Herausforderungen gibt es zahlreiche strategische Chancen. Die Nachfrage nach Hochleistungsrechnern, KI-Beschleunigern und fortschrittlichen Mobilgeräten treibt die rasche Akzeptanz von gestapelten Chiplösungen voran. Unternehmen, die in eigenes Wärme-Management, fortschrittliche Test- und robuste Lieferkettenstrategien investieren, können sich differenzieren und Premiumsegmente des Marktes erobern. Darüber hinaus ermöglichen Partnerschaften zwischen Foundries, OSATs (Outsourced Semiconductor Assembly and Test) und EDA (Electronic Design Automation)-Anbietern neue Design- und Herstellungsparadigmen, wie chipletbasierte Architekturen, die zusätzlichen Wert freisetzen können (TSMC).

- Wärme-Management und Zuverlässigkeit bleiben die wichtigsten technischen Hürden.

- Die Ausbeuteverluste und Inspektionskosten steigen mit zunehmender Integrationskomplexität.

- Risiken in der Lieferkette werden durch geopolitische und logistische Faktoren verstärkt.

- Strategische Investitionen in F&E, Partnerschaften und Resilienz der Lieferkette bieten Wettbewerbsvorteile.

Quellen & Referenzen

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights