Relatório do Mercado de Embalagens em Microeletrônica com Die Empilhados 2025: Crescimento, Mudanças Tecnológicas e Insights Estratégicos para os Próximos 5 Anos. Explore as Principais Tendências, Previsões e Dinâmicas Competitivas que Estão Moldando a Indústria.

- Resumo Executivo & Visão Geral do Mercado

- Principais Tendências Tecnológicas em Embalagens de Microeletrônica com Die Empilhados

- Cenário Competitivo e Principais Jogadores

- Previsões de Crescimento do Mercado (2025–2030): CAGR, Análise de Receita e Volume

- Análise do Mercado Regional: América do Norte, Europa, Ásia-Pacífico e Resto do Mundo

- Perspectivas Futuras: Aplicações Emergentes e Pontos de Investimento

- Desafios, Riscos e Oportunidades Estratégicas

- Fontes & Referências

Resumo Executivo & Visão Geral do Mercado

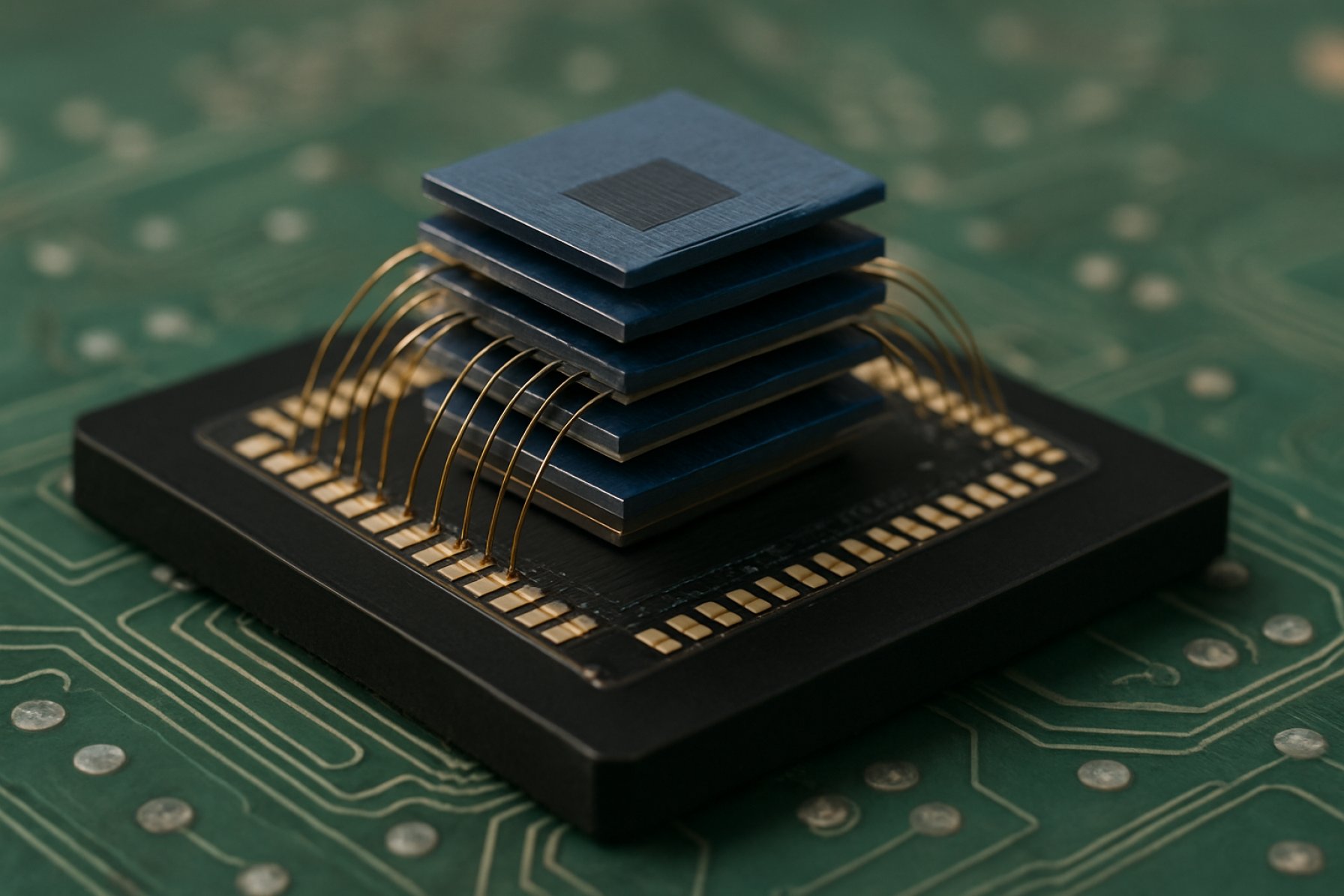

A embalagem de microeletrônica com die empilhados refere-se à integração de múltiplos chips semicondutores dentro de um único pacote, organizados verticalmente para otimizar espaço, desempenho e funcionalidade. Esta tecnologia avançada de embalagem é crucial para atender à crescente demanda por miniaturização, maior desempenho e eficiência energética em setores como eletrônicos de consumo, automotivo, telecomunicações e centros de dados. Em 2025, o mercado global para embalagem de microeletrônica com die empilhados está vivendo um crescimento robusto, impulsionado pela proliferação de dispositivos 5G, aplicações de inteligência artificial (IA) e Internet das Coisas (IoT).

De acordo com a Gartner, o mercado de embalagem de die empilhado deve alcançar uma taxa de crescimento anual composta (CAGR) superior a 8% entre 2023 e 2027, com as receitas previstas para ultrapassar US$ 12 bilhões até 2025. Esse crescimento é sustentado pela adoção crescente de circuitos integrados 3D (3D ICs), soluções de sistemas em pacote (SiP) e módulos de memória de alta largura de banda (HBM), todos os quais aproveitam arquiteturas de die empilhados para oferecer desempenho aprimorado e fatores de forma reduzidos.

Jogadores-chave da indústria, como TSMC, Samsung Electronics e Intel Corporation, estão investindo pesadamente em pesquisa e desenvolvimento para avançar nas tecnologias de vias através do silício (TSV) e embalagem em nível de wafer (WLP). Essas inovações estão possibilitando maiores densidades de interconexão, melhor gerenciamento térmico e menor consumo de energia, que são críticos para aplicações de próxima geração em aceleradores de IA, sistemas avançados de assistência ao condutor (ADAS) e computação de alto desempenho (HPC).

Regionalmente, a Ásia-Pacífico domina o mercado de embalagem de die empilhados, representando mais de 60% da capacidade de produção global, principalmente devido à presença de fundições líderes e fornecedores de OSAT (serviços de montagem e teste de semicondutores terceirizados) em países como Taiwan, Coreia do Sul e China. A América do Norte e a Europa também estão testemunhando uma adoção crescente, particularmente em eletrônicos automotivos e infraestrutura de centros de dados, conforme observado pela IC Insights.

Em resumo, a embalagem de microeletrônica com die empilhados é uma tecnologia fundamental para a evolução da indústria de semicondutores em 2025, permitindo maior integração, desempenho e eficiência em uma ampla gama de aplicações. A trajetória do mercado é moldada por avanços tecnológicos contínuos, investimentos estratégicos de players líderes e a demanda implacável por sistemas eletrônicos mais inteligentes, menores e mais poderosos.

Principais Tendências Tecnológicas em Embalagens de Microeletrônica com Die Empilhados

A embalagem de microeletrônica com die empilhados está na vanguarda da inovação em semicondutores, possibilitando maior desempenho dos dispositivos, funcionalidade aumentada e fatores de forma reduzidos através da integração vertical de múltiplos chips semicondutores dentro de um único pacote. À medida que a indústria avança para 2025, várias tendências tecnológicas-chave estão moldando a evolução e a adoção de soluções de embalagem de die empilhados.

- Integração Avançada de Vias Através do Silício (TSV): A tecnologia TSV continua sendo um pilar para empilhamento de die de alta densidade, oferecendo interconexões de baixa latência e alta largura de banda entre die alinhados verticalmente. Em 2025, os fabricantes estão refinando os processos de TSV para reduzir o diâmetro e o pitch das vias, aumentando assim a densidade de interconexão e melhorando o desempenho elétrico. Isso é particularmente crítico para computação de alto desempenho (HPC) e aplicações de inteligência artificial (IA), onde a largura de banda da memória é um gargalo. A TSMC e a Samsung Electronics estão liderando a comercialização de embalagens avançadas baseadas em TSV de 2.5D e 3D IC.

- Técnicas de Hibridização: A hibridização, que combina a soldagem direta de cobre a cobre e a soldagem dielétrica a dielétrica, está ganhando força como um método para alcançar interconexões ultra-finas e características elétricas melhoradas. Esta tecnologia está permitindo empilhamentos de pitch sub-10 micrômetros, que são essenciais para a integração lógica/memória de próxima geração. A Amkor Technology e a Intel Corporation anunciaram investimentos significativos em hibridização tanto para dispositivos de memória quanto para lógica.

- Integração Heterogênea: A tendência de integrar chiplets diversos—como lógica, memória, RF e analógico—dentro de um único pacote empilhado está acelerando. Essa abordagem permite nodos de processo otimizados para cada função, melhorando o desempenho geral do sistema e a eficiência energética. A associação da indústria SEMI destaca a integração heterogênea como um facilitador chave para soluções avançadas em automóveis, 5G e computação de borda.

- Inovações em Gerenciamento Térmico: À medida que o empilhamento de die aumenta a densidade de potência, materiais avançados de interface térmica (TIMs), refrigeração microfluídica e dissipadores de calor integrados estão sendo desenvolvidos para gerenciar a dissipação de calor. O Yole Group relata que um gerenciamento térmico eficaz é agora um diferenciador primário no design de pacotes de die empilhados, especialmente para os mercados de centros de dados e aceleradores de IA.

- Testes e Inspeção Automatizados: A complexidade dos assemblies de die empilhados exige soluções avançadas de teste e inspeção, incluindo raios-X de alta resolução e detecção de defeitos por IA. A KLA Corporation e a Teradyne estão expandindo suas ofertas para resolver os desafios únicos da confiabilidade e produtividade de pacotes multi-die.

Essas tendências tecnológicas estão coletivamente impulsionando o mercado de embalagem de microeletrônica com die empilhados em direção a uma maior integração, desempenho e confiabilidade, posicionando-o como um facilitador crítico para sistemas eletrônicos de próxima geração em 2025 e além.

Cenário Competitivo e Principais Jogadores

O cenário competitivo do mercado de embalagem de microeletrônica com die empilhados em 2025 é caracterizado por intensa inovação, parcerias estratégicas e um foco em capacidades avançadas de fabricação. Este setor é impulsionado pela demanda por maior desempenho do dispositivo, miniaturização e integração em aplicações como smartphones, computação de alto desempenho, eletrônicos automotivos e dispositivos IoT. Jogadores-chave estão aproveitando sua experiência em embalagem em nível de wafer, tecnologia TSV e integração heterogênea para manter uma vantagem competitiva.

Liderando o mercado estão fornecedores estabelecidos de serviços de embalagem e montagem de semicondutores, incluindo A Amkor Technology, A ASE Technology Holding e TSMC. Essas empresas fizeram investimentos significativos em P&D e capacidade de produção para apoiar a fabricação em alta volume de soluções de die empilhado. Por exemplo, as tecnologias avançadas CoWoS (Chip-on-Wafer-on-Substrate) e SoIC (System on Integrated Chips) da TSMC são amplamente adotadas para computação de alta performance e aplicações de IA, enquanto A Amkor Technology e A ASE Technology Holding oferecem um portfólio amplo de serviços de embalagem 2.5D e 3D para mercados de consumo e empresariais.

Os IDMs (Fabricantes de Dispositivos Integrados) como Intel Corporation e Samsung Electronics também são proeminentes, integrando a embalagem de die empilhados em suas folhas de produtos para melhorar o desempenho dos chips e a eficiência energética. A tecnologia Foveros da Intel e a plataforma X-Cube da Samsung exemplificam abordagens proprietárias para integração vertical e arquiteturas baseadas em chiplet.

Jogadores emergentes e especialistas de nicho, incluindo JCET Group e Powertech Technology Inc., estão ganhando força ao oferecer soluções personalizadas e direcionar setores específicos, como eletrônicos automotivos e industriais. Essas empresas frequentemente colaboram com empresas de semicondutores fabless e integradores de sistemas para entregar pacotes de die empilhados sob medida.

O ambiente competitivo é ainda moldado pela atividade contínua de M&A, licenciamento de tecnologia e joint ventures, à medida que as empresas buscam expandir suas capacidades e alcance global. Segundo o Yole Group, o mercado deve passar por uma consolidação contínua, com os principais jogadores investindo em interconexões de próxima geração, materiais avançados e automação para atender às necessidades em evolução dos mercados de IA, 5G e computação de borda.

Previsões de Crescimento do Mercado (2025–2030): CAGR, Análise de Receita e Volume

O mercado de embalagem de microeletrônica com die empilhados está posicionado para um crescimento robusto entre 2025 e 2030, impulsionado pela demanda crescente por dispositivos eletrônicos miniaturizados e de alto desempenho em aplicações de eletrônicos de consumo, automotivos e centros de dados. De acordo com projeções da MarketsandMarkets, espera-se que o mercado global de IC 3D e embalagem de die empilhados registre uma taxa de crescimento anual composta (CAGR) de aproximadamente 12% durante este período. Essa trajetória de crescimento é sustentada pela adoção crescente de soluções de embalagem avançadas para abordar as limitações das arquiteturas 2D tradicionais, particularmente em termos de eficiência energética, fator de forma e largura de banda.

As previsões de receita indicam que o segmento de embalagem de microeletrônica com die empilhados superará USD 15 bilhões até 2030, de um estimado de USD 8,5 bilhões em 2025. Esse aumento é atribuído à proliferação de inteligência artificial (IA), infraestrutura 5G e computação de borda, todos os quais exigem maior densidade de interconexão e melhor gerenciamento térmico—vantagens chave oferecidas pelas arquiteturas de die empilhados. A Gartner destaca que a mudança da indústria de semicondutores em direção à integração heterogênea e soluções de sistema em pacote (SiP) acelerará ainda mais a adoção das tecnologias de embalagem de die empilhados.

Em termos de volume, o número de unidades de die empilhados enviadas deve crescer a uma CAGR de 13–14% de 2025 a 2030, refletindo tanto a penetração aumentada em dispositivos de consumo de alto volume quanto o uso em expansão em eletrônicos automotivos e IoT industrial. O Yole Group relata que as principais fundições e OSATs (fornecedores de Montagem e Teste de Semicondutores Terceirizados) estão aumentando os investimentos em linhas de embalagem avançadas para atender a essa demanda antecipada, com a Ásia-Pacífico permanecendo o principal centro de produção devido ao seu ecossistema estabelecido de fabricação de semicondutores.

- CAGR (2025–2030): 12–14%

- Receita (2030): USD 15+ bilhões

- Crescimento de Volume: Impulsionado por eletrônicos de consumo, automotivos e aplicações de centros de dados

- Regiões Chave: A Ásia-Pacífico lidera, seguida pela América do Norte e Europa

No geral, o mercado de embalagem de microeletrônica com die empilhados está preparado para uma expansão significativa, impulsionada pela inovação tecnológica e pela busca implacável por maior desempenho e integração em sistemas eletrônicos de próxima geração.

Análise do Mercado Regional: América do Norte, Europa, Ásia-Pacífico e Resto do Mundo

O mercado global de embalagem de microeletrônica com die empilhados está passando por um crescimento dinâmico, com tendências regionais moldadas pela inovação tecnológica, demanda dos usuários finais e desenvolvimentos na cadeia de suprimentos. Em 2025, as regiões da América do Norte, Europa, Ásia-Pacífico e Resto do Mundo (RoW) apresentam características de mercado e motores de crescimento distintos.

- América do Norte: O mercado norte-americano é impulsionado por robustos investimentos em fabricação avançada de semicondutores e uma forte presença de empresas de tecnologia líderes. A região se beneficia de atividades significativas de P&D, particularmente nos Estados Unidos, onde o impulso pela produção doméstica de chips é apoiado por iniciativas governamentais como a Lei CHIPS. Aplicações-chave incluem computação de alto desempenho, eletrônicos automotivos e sistemas de defesa. Segundo a Associação da Indústria de Semicondutores, espera-se que a América do Norte mantenha um crescimento constante na embalagem de die empilhados, impulsionado pela demanda por soluções miniaturizadas e de alta densidade em IA e infraestrutura 5G.

- Europa: O mercado europeu é caracterizado por um foco em aplicações automotivas, automação industrial e IoT. A ênfase da região na qualidade e confiabilidade, junto com normas regulatórias rigorosas, favorece a adoção de tecnologias avançadas de embalagem. Iniciativas como a Lei Europeia dos Chips visam fortalecer as capacidades locais de semicondutores. De acordo com a SEMI, os fabricantes europeus estão investindo cada vez mais em soluções de die empilhados para apoiar os crescentes setores de veículos elétricos e fabricação inteligente da região.

- Ásia-Pacífico: A Ásia-Pacífico domina o mercado global de embalagem de microeletrônica com die empilhados, representando a maior participação em 2025. Essa liderança é sustentada pela presença de fundições e fornecedores de OSAT (serviços de montagem e teste de semicondutores terceirizados) em países como Taiwan, Coreia do Sul, China e Japão. A rápida adoção de eletrônicos de consumo, smartphones e centros de dados na região alimenta a demanda por embalagens de alta densidade. Segundo a IC Insights, o crescimento do mercado da Ásia-Pacífico é ainda acelerado por incentivos governamentais e expansões de capacidade agressivas por parte de players líderes.

- Resto do Mundo (RoW): O segmento RoW, incluindo América Latina, Oriente Médio e África, permanece incipiente, mas mostra potencial de crescimento à medida que as iniciativas de transformação digital se expandem. Investimentos em infraestrutura de telecomunicações e em centros emergentes de fabricação eletrônica devem gradualmente aumentar a demanda por soluções de embalagem de die empilhados, conforme observado pela Gartner.

De modo geral, as dinâmicas regionais em 2025 refletem uma convergência de inovação, apoio político e demanda do mercado final, com a Ásia-Pacífico liderando em volume e a América do Norte e a Europa concentrando-se em aplicações especializadas de alto valor.

Perspectivas Futuras: Aplicações Emergentes e Pontos de Investimento

As perspectivas futuras para a embalagem de microeletrônica com die empilhados em 2025 são moldadas por avanços rápidos na integração de semicondutores, a proliferação de IA e computação de alto desempenho, e a crescente demanda por sistemas eletrônicos miniaturizados e de alta densidade. A embalagem de die empilhados, que envolve a integração vertical de múltiplos chips semicondutores dentro de um único pacote, está sendo cada vez mais reconhecida como um facilitador chave para dispositivos de próxima geração em vários setores de alto crescimento.

As aplicações emergentes são particularmente proeminentes em centros de dados, infraestrutura 5G e computação de borda. A necessidade de maior largura de banda e menor latência nesses ambientes está impulsionando a adoção de arquiteturas de die empilhados 2.5D e 3D, que oferecem desempenho elétrico aprimorado e redução dos comprimentos de interconexão. Em 2025, a integração de memória de alta largura de banda (HBM) com die lógicos deve acelerar, apoiando as demandas computacionais de aceleradores de IA e processadores gráficos avançados. Empresas como Samsung Electronics e TSMC estão investindo pesadamente em linhas de embalagem avançadas para atender a essa demanda.

Outra aplicação emergente é no setor automotivo, onde a embalagem de die empilhados está possibilitando o desenvolvimento de módulos compactos e de alta confiabilidade para sistemas avançados de assistência ao condutor (ADAS) e veículos autônomos. Os rígidos requisitos da indústria automotiva em termos de gerenciamento térmico e confiabilidade estão impulsionando a inovação nas tecnologias de vias através do silício (TSV) e embalagem em nível de wafer, com fornecedores como Infineon Technologies e NXP Semiconductors expandindo seus portfólios para atender a essas necessidades.

Os pontos de investimento em 2025 devem se concentrar na Ásia-Pacífico, particularmente em Taiwan, Coreia do Sul e China, onde os incentivos governamentais e os robustos ecossistemas de fundições estão acelerando P&D e expansão de capacidade. Segundo a Gartner, espera-se que o mercado global de embalagens avançadas cresça a uma CAGR de mais de 7% até 2025, com soluções de die empilhados representando uma parte significativa desse crescimento. Capital de risco e investimentos estratégicos também estão fluindo para startups que desenvolvem novos materiais de interconexão e técnicas de integração heterogênea, conforme destacado por rodadas de financiamento recentes monitoradas pela CB Insights.

- IA e HPC: Embalagem de die empilhados para aceleradores de IA e GPUs

- Automotivo: Módulos compactos e de alta confiabilidade para ADAS e VE

- 5G/Borda: Soluções de baixa latência e alta largura de banda para infraestrutura de rede

- Ásia-Pacífico: Região líder em investimento e expansão da fabricação

Em resumo, 2025 verá a embalagem de microeletrônica com die empilhados na vanguarda da inovação em semicondutores, com forte impulso em IA, automotivo e comunicações, e atividade de investimento significativa na Ásia-Pacífico e em startups de materiais avançados.

Desafios, Riscos e Oportunidades Estratégicas

A embalagem de microeletrônica com die empilhados, um pilar da integração avançada de semicondutores, enfrenta uma paisagem complexa de desafios e riscos em 2025, mas também apresenta oportunidades estratégicas significativas para os jogadores da indústria. O principal desafio técnico continua sendo o gerenciamento térmico. À medida que mais dies são integrados verticalmente, a dissipação de calor se torna cada vez mais problemática, arriscando a confiabilidade do dispositivo e a degradação do desempenho. Materiais avançados de interface térmica e designs inovadores de dissipadores de calor estão sendo explorados, mas sua integração adiciona custo e complexidade ao processo de fabricação (SEMI).

Os riscos de rendimento e confiabilidade também são aumentados em arquiteturas de die empilhados. O número crescente de interconexões, como vias através do silício (TSVs), eleva a probabilidade de defeitos, impactando o rendimento geral. Além disso, a integração heterogênea—combinando dies de diferentes nós de processo ou fundições—introduz desafios de compatibilidade e teste. A necessidade de ferramentas avançadas de inspeção e metrologia está crescendo, mas essas soluções podem aumentar significativamente o capital necessário (TechInsights).

A complexidade na cadeia de suprimentos é outro risco crítico. A embalagem de die empilhados muitas vezes requer colaboração entre múltiplos fornecedores para wafers, substratos e serviços de montagem. Disrupções em qualquer segmento podem atrasar a produção e aumentar custos. Tensões geopolíticas e controles de exportação, particularmente no comércio tecnológico entre EUA e China, exacerbam ainda mais as vulnerabilidades da cadeia de suprimentos (Gartner).

Apesar desses desafios, oportunidades estratégicas abundam. A demanda por computação de alto desempenho, aceleradores de IA e dispositivos móveis avançados está impulsionando a rápida adoção de soluções de die empilhados. Empresas que investem em gerenciamento térmico proprietário, testes avançados e estratégias robustas de cadeia de suprimentos podem se diferenciar e capturar segmentos de mercado premium. Além disso, parcerias entre fundições, OSATs (Serviços de Montagem e Teste de Semicondutores Terceirizados) e fornecedores de EDA (Automação de Design Eletrônico) estão possibilitando novos paradigmas de design e fabricação, como arquiteturas baseadas em chiplet, que podem liberar ainda mais valor (TSMC).

- O gerenciamento térmico e a confiabilidade continuam a ser os principais obstáculos técnicos.

- A perda de rendimento e os custos de inspeção estão aumentando com a maior complexidade na integração.

- Os riscos da cadeia de suprimentos são amplificados por fatores geopolíticos e logísticos.

- Investimentos estratégicos em P&D, parcerias e resiliência na cadeia de suprimentos oferecem vantagens competitivas.

Fontes & Referências

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights