2025 Stacked Die Microelectronics Packaging Market Report: Vækst, Teknologiske Skift, og Strategiske Indsigter for de Næste 5 År. Udforsk Nøgletrends, Fremskrivninger, og Konkurrencedygtige Dynamikker, der Former Industrien.

- Ledelsesresumé & Markedsoversigt

- Nøgleteknologitrends i Stacked Die Mikroelektronikemballering

- Konkurrencelandskab og Ledende Aktører

- Fremskrivninger for Markedsvækst (2025–2030): CAGR, Indtægter, og Volumanalyse

- Regional Markedsanalyse: Nordamerika, Europa, Asien-Stillehavet, og Resten af Verden

- Fremtidsudsigter: Nye Applikationer og Investeringshotspots

- Udfordringer, Risici, og Strategiske Muligheder

- Kilder & Referencer

Ledelsesresumé & Markedsoversigt

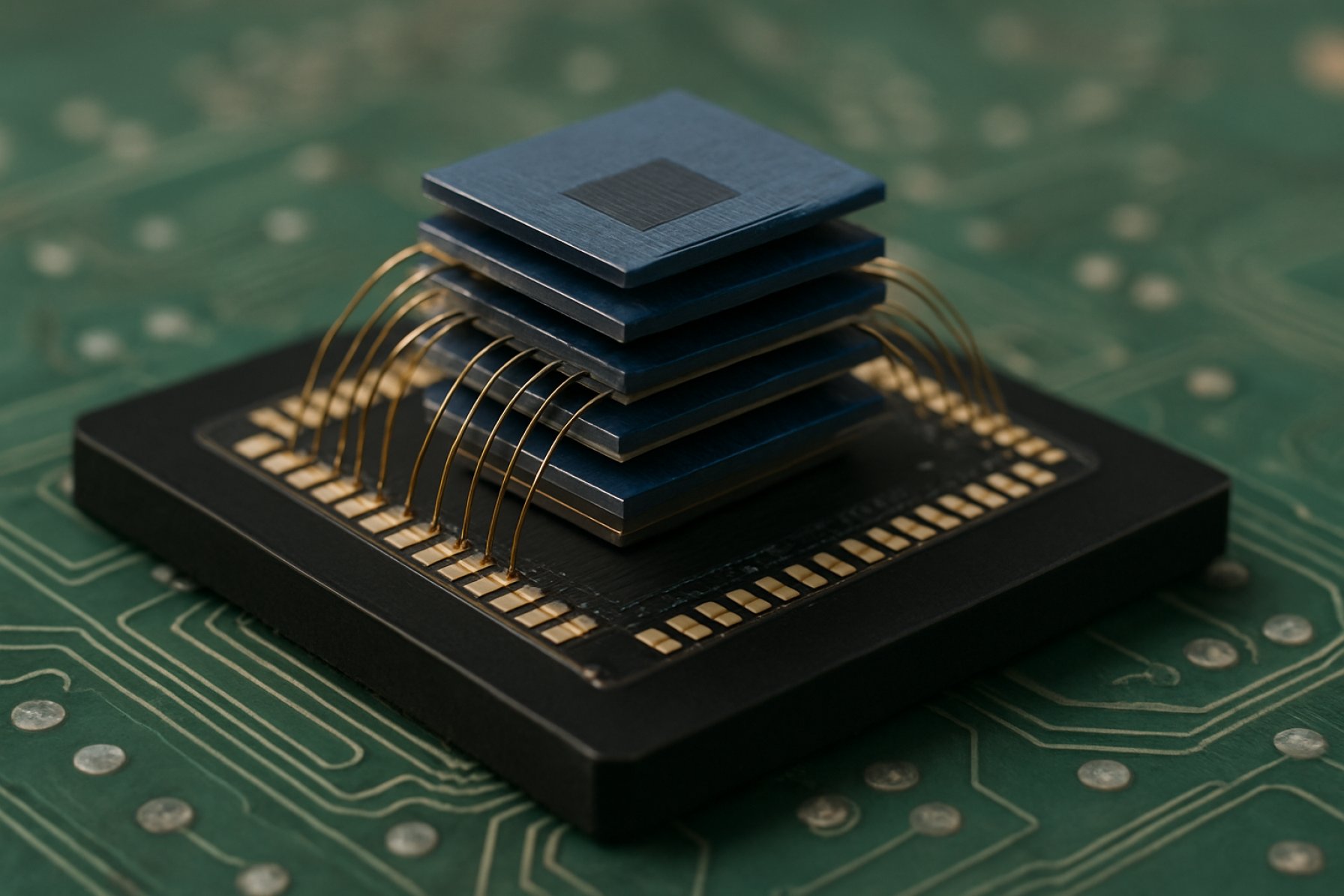

Stacked die mikroelektronikemballering refererer til integrationen af flere halvleder dies inden for en enkelt pakke, arrangeret vertikalt for at optimere plads, ydeevne, og funktionalitet. Denne avancerede emballageteknologi er afgørende for at imødekomme de stigende krav til miniaturisering, højere ydeevne, og energieffektivitet i sektorer som forbrugerelektronik, bilindustri, telekommunikation, og datacentre. Pr. 2025 oplever det globale marked for stacked die mikroelektronikemballering robust vækst, drevet af den stigende udbredelse af 5G-enheder, kunstig intelligens (AI) applikationer, og Internet of Things (IoT).

Ifølge Gartner forventes markedet for stacked die emballering at opnå en sammensat årlig vækstrate (CAGR) på over 8% mellem 2023 og 2027, med indtægter forventet at overstige 12 milliarder dollars inden 2025. Denne vækst er understøttet af den stigende adoption af 3D integrerede kredsløb (3D IC’er), system-in-pakke (SiP) løsninger, og hukommelse med høj båndbredde (HBM) moduler, som alle udnytter stacked die arkitekturer for at levere forbedret ydeevne og reducerede formfaktorer.

Nøgleaktører i branchen som TSMC, Samsung Electronics, og Intel Corporation investerer massivt i forskning og udvikling for at fremme gennem-silicon via (TSV) og wafer-level emballering (WLP) teknologier. Disse innovationer gør det muligt at opnå højere interconnect densiteter, forbedret termisk håndtering, og lavere strømforbrug, hvilket er afgørende for næste generations applikationer inden for AI accelerators, avancerede førerassistent systemer (ADAS), og high-performance computing (HPC).

Regionalt dominerer Asien-Stillehavet markedet for stacked die emballering, som står for mere end 60% af den globale produktionskapacitet, primært på grund af tilstedeværelsen af førende foundries og OSAT (outsourcet halvledermontering og test) udbydere i lande som Taiwan, Sydkorea, og Kina. Nordamerika og Europa oplever også en stigende adoption, især inden for bil-elektronik og datacenterinfrastruktur, som noteret af IC Insights.

Sammenfattende er stacked die mikroelektronikemballering en hjørnestensteknologi for halvlederindustriens evolution i 2025, der muliggør højere integration, ydeevne, og effektivitet på tværs af et bredt spektrum af applikationer. Markedets bane formes af løbende teknologiske fremskridt, strategiske investeringer fra førende aktører, og den utrættelige efterspørgsel efter smartere, mindre, og mere kraftfulde elektroniske systemer.

Nøgleteknologitrends i Stacked Die Mikroelektronikemballering

Stacked die mikroelektronikemballering er i front for halvlederinnovation, der muliggør højere enhedsydeevne, øget funktionalitet, og reducerede formfaktorer ved vertikalt at integrere flere halvleder dies inden for en enkelt pakke. I takt med at branchen bevæger sig ind i 2025 er flere nøgleteknologitrends ved at forme udviklingen og adoptionen af stacked die emballageløsninger.

- Avanceret Gennem-Silicon Via (TSV) Integration: TSV-teknologien forbliver en hjørnesten for høj-densitets die stabling, som tilbyder lav-latens, høj-båndbredde interconnects mellem vertikalt justerede dies. I 2025 finpudser producenterne TSV-processer for at reducere via diameter og pitch, hvilket øger interconnect densiteten og forbedrer elektrisk ydeevne. Dette er særligt kritisk for high-performance computing (HPC) og kunstig intelligens (AI) applikationer, hvor hukommelsesbåndbredde er en flaskehals. TSMC og Samsung Electronics fører an i kommercialiseringen af avanceret TSV-baseret 2.5D og 3D IC emballering.

- Hybrid Bonding Teknikker: Hybrid bonding, som kombinerer direkte kobber-til-kobber og dielektrisk-til-dielektrisk bonding, vinder indpas som en metode til at opnå ultrafine pitch interconnects og forbedrede elektriske egenskaber. Denne teknologi muliggør stabling med mindre end 10 mikron pitch, hvilket er essentielt for næste generations logisk-hukommelse integration. Amkor Technology og Intel Corporation har annonceret betydelige investeringer i hybrid bonding for både hukommelses- og logiske enheder.

- Heterogen Integration: Tendenserne mod at integrere forskellige chiplets—såsom logik, hukommelse, RF, og analog—inden for en enkelt stabelpakke accelererer. Denne tilgang tillader optimerede procesnoder for hver funktion, hvilket forbedrer det overordnede systemets ydeevne og energieffektivitet. SEMI brancheforeningen fremhæver heterogen integration som en nøglemulighed for avancerede bil-, 5G-, og edge computing-løsninger.

- Termisk Håndtering Innovationer: Efterhånden som die stabling øger effekttætheden, udvikles avancerede termiske grænsefladematerialer (TIM’er), mikrofluidisk køling og integrerede varmespredere for at håndtere varmeafledning. Yole Group rapporterer, at effektiv termisk håndtering nu er en primær differentierer i designet af stacked die pakker, især for datacenter- og AI accelerator-markeder.

- Automatiseret Test og Inspektion: Komplekse stacked die samlinger kræver avancerede test- og inspektionsløsninger, herunder højopløselig røntgen og AI-drevet fejlregistrering. KLA Corporation og Teradyne udvider deres tilbud for at imødekomme de unikke udfordringer ved pålidelighed og udbytte af multi-die pakker.

Disse teknologitrends driver samlet set markedet for stacked die mikroelektronikemballering mod større integration, ydeevne, og pålidelighed, hvilket placerer det som en kritisk muliggører for næste generations elektroniske systemer i 2025 og fremover.

Konkurrencelandskab og Ledende Aktører

Det konkurrencedygtige landskab for markedet for stacked die mikroelektronikemballering i 2025 er præget af intens innovation, strategiske partnerskaber, og et fokus på avancerede fremstillingskapaciteter. Denne sektor drives af efterspørgslen efter højere enhedsydeevne, miniaturisering, og integration i applikationer som smartphones, high-performance computing, bil-elektronik, og IoT-enheder. Nøglespillere udnytter deres ekspertise inden for wafer-level emballering, gennem-silicon via (TSV) teknologi, og heterogen integration for at opretholde en konkurrencefordel.

Førende inden for markedet er etablerede tjenesteudbydere inden for halvlederemballering og -samling, herunder Amkor Technology, ASE Technology Holding, og TSMC. Disse virksomheder har foretaget betydelige investeringer i F&U og produktionskapacitet for at støtte højvolumen produktion af stacked die-løsninger. For eksempel anvendes TSMC’s avancerede CoWoS (Chip-on-Wafer-on-Substrate) og SoIC (System on Integrated Chips) teknologier bredt inden for high-end computing og AI-applikationer, mens Amkor Technology og ASE Technology Holding tilbyder en bred portefølje af 2.5D og 3D emballagetjenester til forbrugs- og virksomhedsmarkeder.

IDM’er (Integrated Device Manufacturers) som Intel Corporation og Samsung Electronics er også fremtrædende, idet de integrerer stacked die emballering i deres produktplaner for at forbedre chip-ydeevne og energieffektivitet. Intels Foveros-teknologi og Samsungs X-Cube platform eksemplificerer proprietære tilgange til vertikal integration og chiplet-baserede arkitekturer.

Nye aktører og niche-specialister, herunder JCET Group og Powertech Technology Inc., vinder frem ved at tilbyde skræddersyede løsninger og målrette specifikke vertikaler som bil- og industriel elektronik. Disse virksomheder samarbejder ofte med fabless halvlederfirmaer og systemintegratorer for at levere skræddersyede stacked die pakker.

Det konkurrencedygtige miljø formes desuden af løbende M&A-aktiviteter, teknologilicensering, og joint ventures, da virksomheder søger at udvide deres kapaciteter og globale rækkevidde. Ifølge Yole Group forventes markedet at se fortsatte konsolideringer, med førende aktører, der investerer i næste generations interconnects, avancerede materialer, og automatisering for at imødekomme de udviklende behov inden for AI, 5G, og edge computing markeder.

Fremskrivninger for Markedsvækst (2025–2030): CAGR, Indtægter, og Volumanalyse

Markedet for stacked die mikroelektronikemballering er klar til robust vækst mellem 2025 og 2030, drevet af den stigende efterspørgsel after højtydende, miniaturiserede elektroniske enheder på tværs af forbrugerelektronik, bilindustri, og datacenterapplikationer. Ifølge fremskrivninger fra MarketsandMarkets forventes det globale 3D IC og stacked die emballeringsmarked at registrere en sammensat årlig vækstrate (CAGR) på ca. 12% i denne periode. Denne vækstbane er understøttet af den stigende adoption af avancerede emballageløsninger til at imødekomme begrænsningerne ved traditionelle 2D arkitekturer, især hvad angår energieffektivitet, formfaktor, og båndbredde.

Indtægtsfremskrivninger indikerer, at segmentet for stacked die mikroelektronikemballering vil overstige USD 15 milliarder inden 2030, op fra et estimeret USD 8.5 milliarder i 2025. Denne stigning tilskrives udbredelsen af kunstig intelligens (AI), 5G infrastruktur, og edge computing, som alle kræver højere interconnect densitet og forbedret termisk håndtering—nøglefordele, som stacked die arkitekturer tilbyder. Gartner fremhæver, at halvlederindustriens skift mod heterogen integration og system-in-pakke (SiP) løsninger yderligere vil accelerere adoptionen af stacked die emballeringsteknologier.

I forhold til volumen er antallet af stackede die-enheder, der sendes, forventet at vokse med en CAGR på 13–14% fra 2025 til 2030, hvilket afspejler både øget penetration i højvolumen forbrugerprodukter og stigende brug i bil-elektronik og industriel IoT. Yole Group rapporterer, at førende foundries og OSATs (Outsourced Semiconductor Assembly and Test providers) øger investeringerne i avancerede emballagelinjer for at imødekomme denne forventede efterspørgsel, med Asien-Stillehavet som den dominerende produktionshub på grund af sit etablerede halvlederproduktionsøkosystem.

- CAGR (2025–2030): 12–14%

- Indtægter (2030): USD 15+ milliarder

- Volumen Vækst: Drevet af forbrugerelektronik, bilindustri, og datacenterapplikationer

- Nøgleregioner: Asien-Stillehavet fører, efterfulgt af Nordamerika og Europa

Overordnet set er markedet for stacked die mikroelektronikemballering klar til betydelig ekspansion, drevet af teknologisk innovation og den utrættelige stræben efter højere ydeevne og integration i næste generations elektroniske systemer.

Regional Markedsanalyse: Nordamerika, Europa, Asien-Stillehavet, og Resten af Verden

Det globale marked for stacked die mikroelektronikemballering oplever dynamisk vækst, med regionale tendenser formet af teknologisk innovation, slutbruger efterspørgsel, og forsyningskædeudviklinger. I 2025 fremviser Nordamerika, Europa, Asien-Stillehavet, og resten af verden (RoW) hver deres distinkte markedskarakteristika og vækstdrivere.

- Nordamerika: Det nordamerikanske marked drives af robuste investeringer i avanceret halvlederproduktion og en stærk tilstedeværelse af førende teknologi virksomheder. Regionen drager fordel af betydelige F&U aktiviteter, især i USA, hvor presset for indenlandsk chipproduktion støttes af regeringsinitiativer som CHIPS Act. Nøgleapplikationer inkluderer high-performance computing, bil-elektronik, og forsvarssystemer. Ifølge Semiconductor Industry Association, forventes Nordamerika at opretholde stabil vækst i stacked die emballering, drevet af efterspørgslen efter miniaturiserede, høj-densitets løsninger i AI og 5G infrastruktur.

- Europa: Europas marked karakteriseres ved fokus på bil-, industriel automation, og IoT-applikationer. Regionens vægt på kvalitet og pålidelighed, sammen med strengere reguleringsstandarder, fremmer adoptionen af avancerede emballageteknologier. Initiativer som den Europæiske Chips Act har til formål at styrke lokale halvlederkapaciteter. Ifølge SEMI investerer europæiske producenter i stigende grad i stacked die løsninger for at støtte regionens voksende elbil- og intelligente fremstillingssektorer.

- Asien-Stillehavet: Asien-Stillehavet dominerer det globale marked for stacked die mikroelektronikemballering, idet regionen står for den største andel i 2025. Dette lederskab understøttes af tilstedeværelsen af store foundries og OSAT (outsourcet halvledermontering og test) udbydere i lande som Taiwan, Sydkorea, Kina, og Japan. Regionens hurtige adoption af forbrugerelektronik, smartphones, og datacentre driver efterspørgslen efter høj-densitets emballering. Ifølge IC Insights accelereres Asien-Stillehavets marked yderligere af statslige incitamenter og aggressive kapacitetsudvidelser fra førende spillere.

- Resten af Verden (RoW): RoW-segmentet, herunder Latinamerika, Mellemøsten, og Afrika, forbliver nascent men viser vækstpotentiale i takt med, at digitale transformationsinitiativer udvides. Investeringer i telekommunikationsinfrastruktur og nye elektronikproduktionscentre forventes gradvist at øge efterspørgslen efter stacked die emballageløsninger, som noteret af Gartner.

Overordnet set afspejler de regionale dynamikker i 2025 en konvergens af innovation, politisk støtte, og efterspørgsel fra slutmarkedet, med Asien-Stillehavet som frontløber i volumen og Nordamerika og Europa fokus på høj værdi, specialiserede applikationer.

Fremtidsudsigter: Nye Applikationer og Investeringshotspots

Fremtidsudsigten for stacked die mikroelektronikemballering i 2025 formes af hurtige fremskridt inden for halvlederintegration, udbredelsen af AI og high-performance computing, samt den stigende efterspørgsel efter miniaturiserede, høj-densitets elektroniske systemer. Stacked die emballering, som involverer vertikal integration af flere halvleder dies inden for en enkelt pakke, anerkendes i stigende grad som en vigtig muliggører for næste generations enheder på tværs af flere hurtigt voksende sektorer.

Nye applikationer er særligt fremtrædende i datacentre, 5G infrastruktur, og edge computing. Behovet for højere båndbredde og lavere latens i disse miljøer driver adoptionen af 2.5D og 3D stacked die arkitekturer, som tilbyder forbedret elektrisk ydeevne og reducerede interconnect længder. I 2025 forventes integrationen af hukommelse med høj båndbredde (HBM) med logiske dies at accelerere, hvilket understøtter de beregningsmæssige krav fra AI accelerators og avancerede grafiske processorer. Virksomheder som Samsung Electronics og TSMC investerer massivt i avancerede emballagelinjer for at imødekomme denne efterspørgsel.

En anden ny applikation er inden for bilsektoren, hvor stacked die emballering muliggør udviklingen af kompakte, høj-pålidelige moduler til avancerede førerassistent systemer (ADAS) og autonome køretøjer. Bilindustriens strenge krav til termisk håndtering og pålidelighed fremmer innovation inden for gennem-silicon via (TSV) og wafer-level emballeringsteknologier, med leverandører som Infineon Technologies og NXP Semiconductors der udvider deres porteføljer for at imødekomme disse behov.

Investeringshotspots i 2025 forventes at centrere sig omkring Asien-Stillehavet, især Taiwan, Sydkorea, og Kina, hvor statslige incitamenter og robuste foundry-økosystemer accelererer F&U og kapacitetsudvidelser. Ifølge Gartner forventes det globale avancerede emballeringsmarked at vokse med en CAGR på over 7% frem til 2025, med stacked die løsninger repræsenterende en betydelig del af denne vækst. Risikovillig kapital og strategiske investeringer strømmer også ind i startups, der udvikler nye interconnect materialer og heterogene integrationsmetoder, som fremhævet af de seneste finansieringsrunder, der følges af CB Insights.

- AI og HPC: Stacked die emballering for AI accelerators og GPU’er

- Bilindustri: Høj-pålidelige, kompakte moduler til ADAS og elbiler

- 5G/Edge: Lav-latens, høj-båndbredde løsninger til netværksinfrastruktur

- Asien-Stillehavet: Ledende region for investering og produktionsudvidelse

Sammenfattende vil 2025 se stacked die mikroelektronikemballering i front for halvlederinnovation, med stærkt momentum inden for AI, bilindustri, og kommunikation, samt betydelig investeringsaktivitet i Asien-Stillehavet og avancerede materialestartups.

Udfordringer, Risici, og Strategiske Muligheder

Stacked die mikroelektronikemballering, en hjørnesten for avanceret halvlederintegration, står overfor et komplekst landskab af udfordringer og risici i 2025, men præsenterer også betydelige strategiske muligheder for aktørerne i industrien. Den primære tekniske udfordring forbliver termisk håndtering. Efterhånden som flere dies integreres vertikalt, bliver varmeafledning stadig mere problematisk, hvilket risikerer enhedens pålidelighed og ydeevnedæmpning. Avancerede termiske grænsefladematerialer og innovative design af varmespredere undersøges, men deres integration tilføjer omkostninger og kompleksitet til fremstillingsprocessen (SEMI).

Udbytte- og pålidelighedsrisici er også forstærket i stacked die arkitekturer. Det øgede antal interconnects, såsom gennem-silicon vias (TSV’er), øger sandsynligheden for fejl, hvilket påvirker det samlede udbytte. Desuden introducerer heterogen integration—kombinere dies fra forskellige procesnoder eller foundries—kompatibilitets- og testudfordringer. Behovet for avancerede inspektions- og metrologiværktøjer vokser, men disse løsninger kan øge kapitaludgifterne betydeligt (TechInsights).

Forsyningskædekompleksitet er en anden kritisk risiko. Stacked die emballering kræver ofte samarbejde mellem flere leverandører for wafers, substrater, og monteringsydelser. Forstyrrelser i ethvert segment kan forsinke produktionen og øge omkostningerne. Geopolitiske spændinger og eksportkontroller, især inden for den amerikansk-kinesiske teknologihandel, forstærker yderligere sårbarheder i forsyningskæden (Gartner).

På trods af disse udfordringer er der strategiske muligheder. Efterspørgslen efter high-performance computing, AI accelerators, og avancerede mobile enheder driver hurtig adoption af stacked die løsninger. Virksomheder, der investerer i proprietær termisk håndtering, avanceret test, og robuste forsyningskædestrategier, kan differentiere sig og fange premium markedsegmenter. Derudover muliggør partnerskaber mellem foundries, OSATs (Outsourced Semiconductor Assembly and Test), og EDA (Electronic Design Automation) udbydere nye design- og fremstillingsparadigmer, såsom chiplet-baserede arkitekturer, hvilket yderligere kan frigøre værdi (TSMC).

- Termisk håndtering og pålidelighed forbliver de største tekniske hindringer.

- Udbytte tab og inspektionsomkostninger stiger med øget integrationskompleksitet.

- Risici i forsyningskæden forstærkes af geopolitiske og logistiske faktorer.

- Strategiske investeringer i F&U, partnerskaber, og forsyningskæde-resiliens tilbyder konkurrencefordele.

Kilder & Referencer

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights