Доклад за пазара на пакетирането на микросхеми с наслагване на чипове за 2025 г.: Растеж, технологични промени и стратегически прозрения за следващите 5 години. Изследвайте ключовите тенденции, прогнози и конкурентна динамика, оформящи индустрията.

- Обобщение и преглед на пазара

- Ключови технологични тенденции в пакетирането на микросхеми с наслагване на чипове

- Конкурентна среда и водещи играчи

- Прогнози за растеж на пазара (2025–2030): CAGR, анализ на приходите и обема

- Регионален анализ на пазара: Северна Америка, Европа, Азия-Тихоокеанския регион и останалия свят

- Бъдеща перспектива: Нови приложения и инвестиционни горещи точки

- Предизвикателства, рискове и стратегически възможности

- Източници и препратки

Обобщение и преглед на пазара

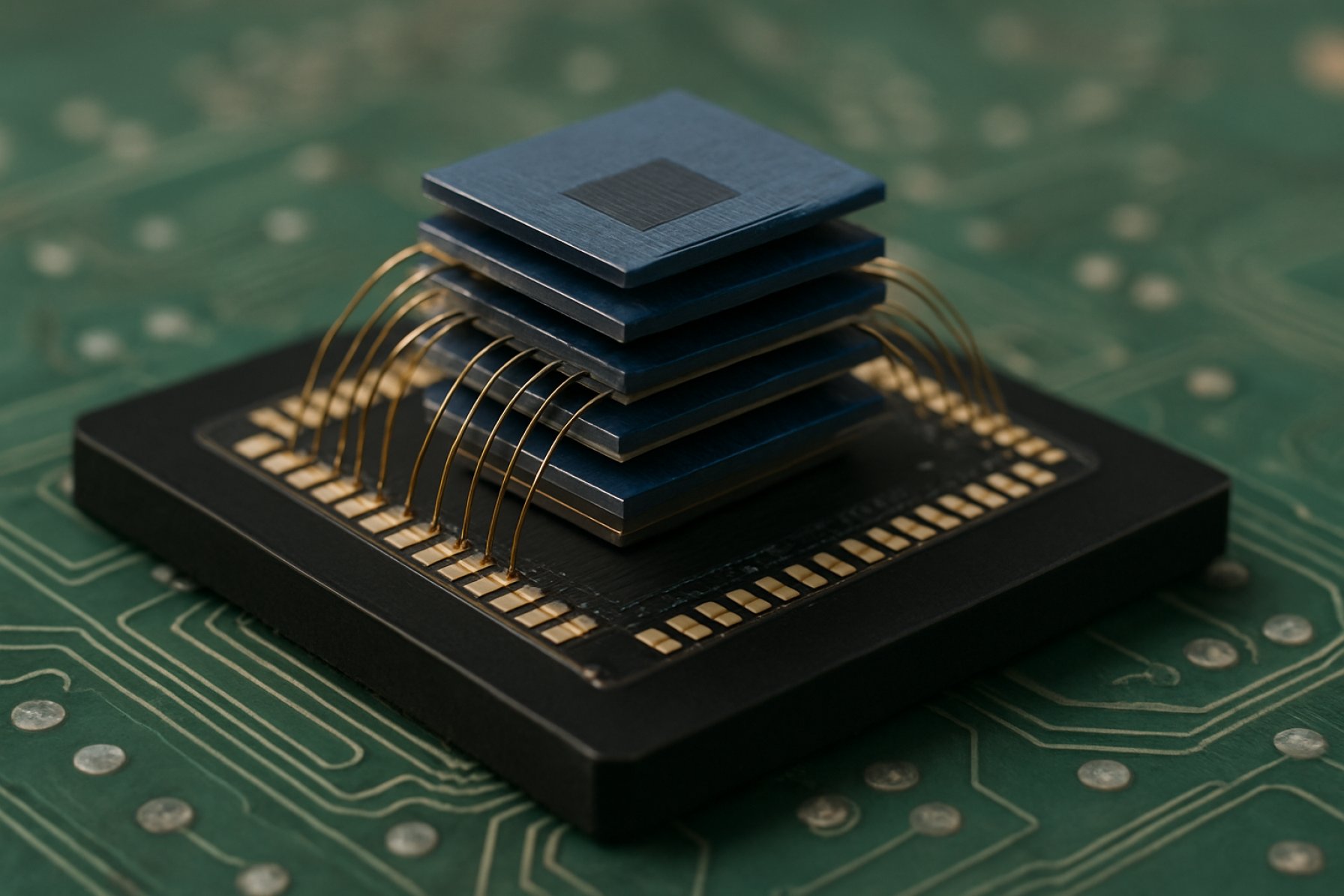

Пакетирането на микросхеми с наслагване на чипове се отнася до интеграцията на множество полупроводникови чипове в един пакет, подредени вертикално, за да се оптимизират пространството, производителността и функционалността. Тази напреднала технология за опаковане е основополагающа за задоволяване на нарастващите изисквания за миниатюризация, по-висока производителност и енергийна ефективност в сектори като потребителска електроника, автомобилостроене, телекомуникации и центрове за данни. Към 2025 г. глобалният пазар на пакетирането на микросхеми с наслагване на чипове преживява силен растеж, подпомаган от разширяването на 5G устройствата, приложенията на изкуствения интелект (AI) и Интернет на нещата (IoT).

Според Gartner, пазарът на пакетирането на микросхеми с наслагване на чипове се прогнозира да постигне средногодишен темп на растеж (CAGR) от над 8% между 2023 и 2027 г., като приходите се очаква да надминат 12 милиарда долара до 2025 г. Този растеж се основава на нарастващото приемане на 3D интегрирани схеми (3D ICs), решенията за система в пакет (SiP) и модули с висока честотна памет (HBM), които използват архитектури с наслагване на чипове за предлагане на подобрена производителност и намалени размери.

Ключови играчи в индустрията като TSMC, Samsung Electronics и Intel Corporation инвестираха значителни средства в научноизследователска и развойна дейност, за да напреднат в технологиите за вертикални свързвания (TSV) и пакетирането на ниво wafer (WLP). Тези иновации позволяват по-високи плътности на свързване, подобрено управление на топлината и по-нисък енергиен разход, което е критично за приложения от следващо поколение в AI ускорители, напреднали системи за помощ при шофиране (ADAS) и високопроизводителни компютри (HPC).

Регионално, Азия-Тихоокеанският регион доминира на пазара на пакетирането на микросхеми с наслагване на чипове, като заема повече от 60% от глобалния производствен капацитет, основно поради наличието на водещи фабрики и доставчици на услуги за опаковане и тест (OSAT) в държави като Тайван, Южна Корея и Китай. Северна Америка и Европа също наблюдават нарастващо приемане, особено в автомобилната електроника и инфраструктурата на центровете за данни, каза IC Insights.

В заключение, пакетирането на микросхеми с наслагване на чипове е основополагаща технология за еволюцията на полупроводниковата индустрия през 2025 г., позволяваща по-висока интеграция, производителност и ефективност в широк спектър от приложения. Траекторията на пазара се оформя от текущите технологични напредъци, стратегическите инвестиции на водещите играчи и неумолимото търсене на по-умни, по-малки и мощни електронни системи.

Ключови технологични тенденции в пакетирането на микросхеми с наслагване на чипове

Пакетирането на микросхеми с наслагване на чипове е в авангарда на иновациите в полупроводниците, позволявайки по-висока производителност на устройствата, увеличена функционалност и намалени размери чрез вертикална интеграция на множество полупроводникови чипове в един пакет. С навлизането на индустрията в 2025 г., няколко ключови технологични тенденции оформят еволюцията и приемането на решения за пакетирането с наслагване на чипове.

- Развита интеграция через силиконови свързвания (TSV): Технологията TSV остава основополагающа за наслагването на чипове с висока плътност, предлагаща ниска латентност и висока честотна свързаност между вертикално подредените чипове. През 2025 г. производителите усъвършенстват процесите на TSV, за да намалят диаметъра и стъпката на свързванията, увеличавайки плътността на свързване и подобрявайки електрическите характеристики. Това е особено критично за високопроизводителни компютри (HPC) и приложения с изкуствен интелект (AI), при които честотната лента на паметта е ограничение. TSMC и Samsung Electronics водят в комерсиализацията на напреднало опаковане на 2.5D и 3D IC на базата на TSV.

- Хибридни технологии за свързване: Хибридното свързване, което комбинира директно свързване на мед до мед и диелектрик до диелектрик, нараства по популярност като метод за постигане на ултра-фини свързвания и подобрени електрически характеристики. Тази технология позволява наслагване с под 10 микрон стъпка, което е съществено за интеграцията на логика и памет от следващо поколение. Amkor Technology и Intel Corporation обявиха значителни инвестиции в хибридно свързване както за памет, така и за логически устройства.

- Хетерогенна интеграция: Тенденцията за интегриране на разнообразни чиплети – като логика, памет, RF и аналогови – в един пакет с наслагване на чипове се ускорява. Този подход позволява оптимизиране на производствените възли за всяка функция, подобрявайки цялостната производителност на системата и енергийната ефективност. Индустриалната асоциация SEMI подчертава хетерогенната интеграция като ключов фактор за напреднали решения в автомобилната индустрия, 5G и крайна компютърна обработка.

- Иновации в управлението на топлината: С нарастващото плътност на мощност в наслагването на чипове, се разработват усъвършенствани термални интерфейсни материали (TIM), микрофлуидно охлаждане и интегрирани термални разпределители, за да се управлява топлинната дисипация. Yole Group съобщава, че ефективното управление на топлината сега е основна диференцираща характеристика в дизайна на пакети с наслагване на чипове, особено за пазара на центрове за данни и AI ускорители.

- Автоматизирано тестване и инспекция: Сложността на сглобките с наслагване на чипове налага напреднали решения за тестване и инспекция, включително високо резолюционни рентгенови и AI-държани системи за откриване на дефекти. KLA Corporation и Teradyne разширяват своите предложения, за да отговорят на уникалните предизвикателства свързани с надеждността на многожичните пакети и доходността.

Тези технологични тенденции колективно управляват пазара на пакетирането на микросхеми с наслагване на чипове към по-голяма интеграция, производителност и надеждност, позиционирайки го като критичен фактор за следващото поколение електронни системи през 2025 г. и след това.

Конкурентна среда и водещи играчи

Конкурентната среда на пазара на пакетирането на микросхеми с наслагване на чипове през 2025 г. е характеризирана от интензивни иновации, стратегически партньорства и фокус върху напреднали производствени възможности. Този сектор е движен от търсенето на по-висока производителност на устройствата, миниатюризация и интеграция в приложения като смартфони, високопроизводителна компютърна обработка, автомобилна електроника и IoT устройства. Ключовите играчи използват своята експертиза в пакетирането на ниво wafer, технологии за вертикални свързвания (TSV) и хетерогенна интеграция, за да поддържат конкурентно предимство.

На пазара водят утвърдени доставчици на опаковане и сглобяване на полупроводници, включително Amkor Technology, ASE Technology Holding и TSMC. Тези компании са направили значителни инвестиции в НИРД и производствени капацитети, за да подкрепят производството на пакети с наслагване на чипове. Например, напредналите технологии на TSMC CoWoS (Chip-on-Wafer-on-Substrate) и SoIC (System on Integrated Chips) са широко приети за високопроизводителни и AI приложения, докато Amkor Technology и ASE Technology Holding предлагат широк портфейл от услуги за 2.5D и 3D опаковане за потребителските и корпоративните пазари.

IDM (Integrated Device Manufacturers) компании, като Intel Corporation и Samsung Electronics, също са видни, интегрирайки пакети с наслагване на чипове в своите продуктов капацитети за подобряване на производителността на чиповете и енергийната им ефективност. Технологията Foveros на Intel и платформата X-Cube на Samsung илюстрират собствени подходи към вертикалната интеграция и архитектури на базата на чиплети.

Нови играчи и ниши специалисти, включително JCET Group и Powertech Technology Inc., придобиват популярност, предлагайки персонализирани решения и фиксирайки се на определени вертикали, като автомобилна и индустриална електроника. Тези компании често си партнират с безфабрични полупроводникови компании и системни интегратори, за да предоставят специфични пакети с наслагване на чипове.

Конкурентната среда се променя допълнително от текущата активност в сливането и придобиването, лицензирането на технологии и съвместни предприятия, тъй като компаниите се стремят да разширят своите възможности и глобален обхват. Според Yole Group, се очаква пазарът да свидетелства за продължаваща консолидация, като водещите играчи инвестират в нови междинни свързвания, напреднали материали и автоматизация, за да отговорят на развиващите се нужди на пазара на AI, 5G и крайни компютри.

Прогнози за растеж на пазара (2025–2030): CAGR, анализ на приходите и обема

Пазарът на пакетирането на микросхеми с наслагване на чипове е готов за силен растеж между 2025 и 2030 г., поддържан от нарастващото търсене на високопроизводителни, миниатюризирани електронни устройства в приложения за потребителска електроника, автомобилостроене и центрове за данни. Според прогнозите на MarketsandMarkets, се очаква глобалният пазар на 3D IC и пакетирането на наслагвани чипове да регистрира средногодишен темп на растеж (CAGR) от приблизително 12% през този период. Тази растежна траектория е основана на нарастващото приемане на напреднали решения за опаковане, за да се справят с ограниченията на традиционните 2D архитектури, особено по отношение на енергийната ефективност, форм-фактор и честотна лента.

Прогнозите за приходите показват, че сегментът на пакетирането на микросхеми с наслагване на чипове ще надвиши 15 милиарда долара до 2030 г., в сравнение с приблизително 8.5 милиарда долара през 2025 г. Този ръст се дължи на разширяването на изкуствения интелект (AI), 5G инфраструктурата и крайна компютърна обработка, всички от които изискват по-висока плътност на свързване и подобрено управление на топлината – ключови предимства, предлагани от архитектурите с наслагване на чипове. Gartner подчертава, че преходът на полупроводниковата индустрия към хетерогенна интеграция и решения за система в пакет (SiP) ще допълнително ускори приемането на технологиите за пакетирането с наслагване на чипове.

По отношение на обема, броят на доставените единици с наслагване на чипове се прогнозира да нарасне с CAGR от 13-14% от 2025 до 2030 г., отразявайки както увеличеното проникване в устройства за масово потребление, така и разширяващата се употреба в автомобилната електроника и индустриалния IoT. Yole Group съобщава, че водещите фабрики и OSAT (доставчици на услуги за опаковане и тест) увеличават инвестициите си в напреднали линии за опаковане, за да отговорят на това предстоящо търсене, като Азия-Тихоокеанския регион остава доминиращ производствен хъб поради утвърдената си екосистема за производство на полупроводници.

- CAGR (2025–2030): 12–14%

- Приходи (2030): над 15 милиарда долара

- Ръст на обема: Движен от електроника за потребителския сегмент, автомобилостроене и центрове за данни

- Ключови региони: Азия-Тихоокеанския регион води, следвана от Северна Америка и Европа

Общо взето, пазарът на пакетирането на микросхеми с наслагване на чипове е готов за значителна експанзия, поддържан от технологични иновации и неумолимо натиск за по-висока производителност и интеграция в електронните системи от следващо поколение.

Регионален анализ на пазара: Северна Америка, Европа, Азия-Тихоокеанския регион и останалия свят

Глобалният пазар на пакетирането на микросхеми с наслагване на чипове преживява динамичен растеж, с регионални тенденции, формулирани от технологични иновации, търсенето от страна на крайния потребител и развитието на веригата за доставки. През 2025 г. Северна Америка, Европа, Азия-Тихоокеанския регион и останалия свят (RoW) предлагат различни характеристики на пазара и фактори за растеж.

- Северна Америка: Пазарът в Северна Америка се движи от силни инвестиции в напреднало производство на полупроводници и силно присъствие на водещи технологични компании. Регионът печели от значителни НИРД дейности, особено в Съединените щати, където подкрепата на правителството, като Закона за чиповете (CHIPS Act), подкрепя местното производство на чипове. Ключови приложения включват високопроизводителна компютърна обработка, автомобилна електроника и отбранителни системи. Според Асоциацията на индустрията на полупроводниците, се очаква Северна Америка да поддържа стабилен растеж в пакетирането с наслагване на чипове, движен от търсенето на миниатюрни, високоплътностни решения в AI и 5G инфраструктура.

- Европа: Европейският пазар е характерен с фокус върху автомобилната, индустриалната автоматизация и IoT приложения. Акцентът върху качеството и надеждността, наред със стриктните регулаторни стандарти, насърчава приемането на напреднали технологии за опаковане. Инициативи като Европейския закон за чиповете целят да подсилят местните способности за полупроводници. Според SEMI, европейските производители все повече инвестират в решения с наслагване на чипове, за да подпомогнат растящия сектор на електрическите превозни средства и интелигентното производство.

- Азия-Тихоокеанския регион: Азия-Тихоокеанският регион доминира на глобалния пазар на пакетирането на микросхеми с наслагване на чипове, заемащ най-голям дял през 2025 г. Тази лидерска позиция се основава на наличието на основни фабрики и доставчици на услуги за опаковане и тест (OSAT) в такива страни като Тайван, Южна Корея, Китай и Япония. Бързото приемане на потребителска електроника, смартфони и центрове за данни в региона предизвиква търсенето на пакети с висока плътност. Според IC Insights, растежът на пазара в Азия-Тихоокеанския регион се ускорява и от правителствени стимули и агресивно разширяване на капацитетите от водещи играчи.

- О restantes от света (RoW): Сегментът RoW, включващ Латинска Америка, Близкия изток и Африка, остава начален, но показва потенциал за растеж, тъй като инициативите за цифрова трансформация се разширяват. Инвестиции в телекомуникационна инфраструктура и нови хъбове за производство на електроника се очаква да увеличат постепенно търсенето на решения за опаковане с наслагване на чипове, както отбелязва Gartner.

Общо взето, регионалната динамика през 2025 г. отразява сблъсък на иновации, политическа подкрепа и търсене на краен пазар, като Азия-Тихоокеанският регион води по обем, а Северна Америка и Европа се фокусират върху високо стойностни, специализирани приложения.

Бъдеща перспектива: Нови приложения и инвестиционни горещи точки

Бъдещата перспектива за пакетирането на микросхеми с наслагване на чипове през 2025 г. е оформена от бързото напредване на интеграцията на полупроводниците, разширението на AI и високопроизводителната компютърна обработка и нарастващото търсене на миниатюризирани, високоплътностни електронни системи. Пакетирането с наслагване на чипове, което включва вертикална интеграция на множество полупроводникови чипове в един пакет, е все по-признато като ключов фактор за следващото поколение устройства в няколко сектора с висок растеж.

Новите приложения са особено предизвикателни в центровете за данни, 5G инфраструктурата и крайна компютърна обработка. Нуждата от по-висока честотна лента и по-ниска латентност в тези среди предизвиква приемането на архитектури с наслагване на чипове 2.5D и 3D, които предлагат подобрена електрическа производителност и намалени дължини на свързването. През 2025 г. интеграцията на памет с висока честотна лента (HBM) с логически чипове се очаква да се ускори, за да поддържа компютърните изисквания на AI ускорители и напреднали графични процесори. Компании като Samsung Electronics и TSMC инвестират значително в напреднали линии за опаковане, за да отговорят на това търсене.

Друго ново приложение е в автомобилния сектор, където пакетирането с наслагване на чипове позволява разширението на компактни, високо надеждни модули за напреднали системи за помощ при шофиране (ADAS) и автономни превозни средства. Строгите изисквания на автомобилната индустрия за управление на топлината и надеждността стимулират иновации в технологиите за вертикални свързвания (TSV) и пакетирането на ниво wafer, като доставчици като Infineon Technologies и NXP Semiconductors разширяват своите портфейли, за да отговорят на тези нужди.

Инвестиционните горещи точки през 2025 г. се очаква да бъдат в Азия-Тихоокеанския регион, особено в Тайван, Южна Корея и Китай, където правителствени стимули и стабилни фабрични екосистеми ускоряват НИРД и разширяване на капацитета. Според Gartner, се прогнозира, че глобалният пазар за напреднало опаковане ще расте с CAGR от над 7% до 2025 г., като решенията с наслагване на чипове представляват значителна част от този растеж. Венчър капитал и стратегически инвестиции също текат в стартиращи компании, разработващи нови материали за свързване и хетерогенни интеграционни техники, както е подчертано от последните кръгове финансиране, проследени от CB Insights.

- AI и HPC: Пакетиране с наслагване на чипове за AI ускорители и GPU

- Автомобили: Компактни модули с висока надеждност за ADAS и електрически превозни средства

- 5G/Edge: Решения с ниска латентност и висока честотна лента за мрежова инфраструктура

- Азия-Тихоокеанския регион: Водещ регион за инвестиции и разширяване на производството

В заключение, 2025 година ще види пакетирането на микросхеми с наслагване на чипове в авангарда на иновациите в полупроводниците, с силни импулси в AI, автомобилната индустрия и комуникациите, и значителна инвестиционна активност в Азия-Тихоокеанския регион и стартиращи компании, разработващи напреднали материали.

Предизвикателства, рискове и стратегически възможности

Пакетирането на микросхеми с наслагване на чипове, основополагающа част от напредналата интеграция на полупроводниците, се сблъсква с комплексна среда от предизвикателства и рискове през 2025 г., но също така предлага значителни стратегически възможности за участниците в индустрията. Основното техническо предизвикателство остава управлението на топлината. С увеличаване на вертикалната интеграция на чиповете, дисипацията на топлина става все по-проблематична, рискувайки надеждността на устройствата и спад на производителността. Изследват се усъвършенствани термални интерфейсни материали и иновационни дизайни на топлинни разпределители, но тяхната интеграция увеличава разходите и сложността на производствения процес (SEMI).

Рисковете от доходността и надеждността също са повишени в архитектурите с наслагване на чипове. Увеличеното количество на свързвания, като вертикални свързвания (TSV), увеличава вероятността от дефекти, влияещи на общата доходност. Освен това, хетерогенната интеграция – комбиниране на чипове от различни производствени възли или фабрики – въвежда предизвикателства за съвместимост и изпитване. Нуждата от усъвършенствани инструменти за инспекция и метролозия нараства, но тези решения могат значително да увеличат капиталовите разходи (TechInsights).

Сложността на веригата на доставки също е критичен риск. Пакетирането с наслагване на чипове често изисква сътрудничество между множество доставчици за wafer, субстрати и услуги за сглобяване. Прекъсвания в който и да е сегмент могат да забавят производството и да увеличат разходите. Геополитическите напрежения и контролите за износ, особено в търговията с технологии между САЩ и Китай, допълнително влошават уязвимостите на веригата на доставки (Gartner).

Въпреки тези предизвикателства, стратегическите възможности са многобройни. Търсенето на високопроизводителни компютри, AI ускорители и напреднали мобилни устройства движи бързото приемане на решения с наслагване на чипове. Компаниите, които инвестират в собствени технологии за управление на топлината, напреднало тестване и стабилни стратегии за веригата на доставки, могат да се разграничат и да завладеят премиум пазарни сегменти. Освен това, партньорствата между фабриките, OSAT (доставчици на услуги за опаковане и тест) и доставчиците на EDA (Автоматизация на електронния дизайн) позволяват нови дизайни и производствени парадигми, като архитектури на базата на чиплети, които могат да отключат допълнителна стойност (TSMC).

- Управлението на топлината и надеждността остават основни технически пречки.

- Загубите от доходност и разходите за инспекция растат с увеличаването на сложността на интеграцията.

- Рискът от веригата на доставки се усилва от геополитически и логистични фактори.

- Стратегическите инвестиции в НИРД, партньорства и устойчивост на веригата на доставки предлагат конкурентни предимства.

Източници и препратки

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Асоциацията на индустрията на полупроводниците

- Infineon Technologies

- NXP Semiconductors

- TechInsights