2025 Trh balení mikroelektroniky s vrstvenými čipy: Růst, technologické změny a strategické poznatky na příštích 5 let. Prozkoumejte klíčové trendy, předpovědi a konkurenční dynamiku formující průmysl.

- Výkonný souhrn a přehled trhu

- Klíčové technologické trendy v balení mikroelektroniky s vrstvenými čipy

- Konkurenční situace a vedoucí hráči

- Předpovědi růstu trhu (2025–2030): CAGR, analýza příjmů a objemu

- Regionální analýza trhu: Severní Amerika, Evropa, Asie a Tichomoří a zbytek světa

- Budoucí vyhlídky: Nově vznikající aplikace a investiční hotspoty

- Výzvy, rizika a strategické příležitosti

- Zdroje a odkazy

Výkonný souhrn a přehled trhu

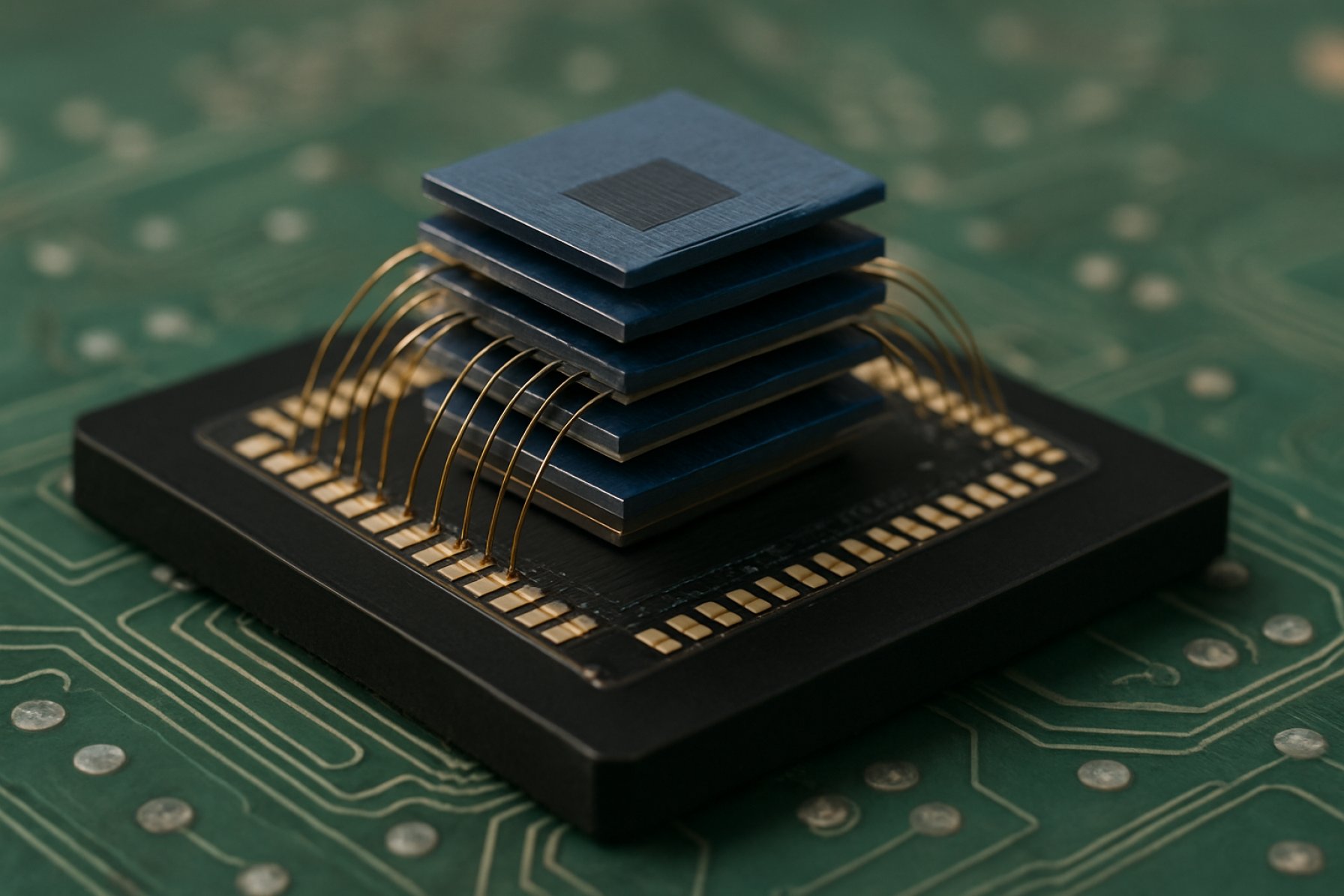

Balení mikroelektroniky s vrstvenými čipy se týká integrace více polovodičových čipů v jedné skříni, uspořádané vertikálně pro optimalizaci prostoru, výkonu a funkčnosti. Tato pokročilá technologie balení je klíčová pro splnění rostoucích požadavků na miniaturizaci, vyšší výkon a energetickou účinnost v oblastech jako jsou spotřební elektronika, automobilový průmysl, telekomunikace a datové centra. V roce 2025 globální trh pro balení mikroelektroniky s vrstvenými čipy zaznamenává silný růst, poháněný proliferací zařízení 5G, aplikacemi umělé inteligence (AI) a Internetem věcí (IoT).

Podle společnosti Gartner se očekává, že trh balení s vrstvenými čipy dosáhne složené roční míry růstu (CAGR) přes 8 % v období 2023–2027, přičemž se příjmy očekávají nad 12 miliard dolarů do roku 2025. Tento růst je podpořen rostoucím přijetím 3D integrovaných obvodů (3D IC), řešeními systémů v balení (SiP) a moduly s vysokou šířkou pásma (HBM), která všechna využívají architektury s vrstvenými čipy k dosažení lepšího výkonu a menších rozměrů.

Klíčoví hráči v odvětví, jako jsou TSMC, Samsung Electronics a Intel Corporation, investují značné prostředky do výzkumu a vývoje, aby pokračovali v pokroku v technologiích přesilových via (TSV) a balení na úrovni waferu (WLP). Tyto inovace umožňují vyšší hustotu propojení, zlepšené řízení tepla a nižší spotřebu energie, což je kritické pro aplikace nové generace v akcelerátorech AI, pokročilých systémech asistence řidičů (ADAS) a vysoce výkonném computingu (HPC).

Regionálně dominuje trh balení s vrstvenými čipy v oblasti Asie a Tichomoří, která představuje více než 60 % globální výrobní kapacity, především díky přítomnosti předních tržišť a poskytovatelů outsourcovaného montáže polovodičů a testování (OSAT) v zemích jako je Tchaj-wan, Jižní Korea a Čína. Severní Amerika a Evropa rovněž zaznamenávají rostoucí přijetí, zejména v automobilové elektronice a infrastruktuře datových center, jak oznámila IC Insights.

Stručně řečeno, balení mikroelektroniky s vrstvenými čipy je základní technologií pro vývoj polovodičového průmyslu v roce 2025, která umožňuje vyšší integraci, výkon a účinnost napříč širokým spektrem aplikací. Trajektorie trhu je formována probíhajícími technologickými pokroky, strategickými investicemi předních hráčů a neúprosně rostoucí poptávkou po inteligentnějších, menších a výkonnějších elektronických systémech.

Klíčové technologické trendy v balení mikroelektroniky s vrstvenými čipy

Balení mikroelektroniky s vrstvenými čipy je v popředí inovací polovodičů, umožňuje vyšší výkon zařízení, zvýšenou funkčnost a redukované rozměry vertikální integrací více polovodičových čipů v jedné skříni. Jak se průmysl posouvá do roku 2025, několik klíčových technologických trendů formuje evoluci a přijetí řešení balení s vrstvenými čipy.

- Pokročilá integrace přesilových via (TSV): Technologie TSV zůstává základem pro balení s vysokou hustotou, nabízející nízko-latentní, vysokobandové propojení mezi vertikálně uspořádanými čipy. V roce 2025 výrobci zpevňují procesy TSV, aby snížili průměr a rozteč via, čímž zvyšují hustotu propojení a zlepšují elektrický výkon. To je obzvlášť kritické pro vysoce výkonný computing (HPC) a aplikace umělé inteligence (AI), kde je šířka pásma paměti úzkým hrdlem. TSMC a Samsung Electronics vedou v komercializaci pokročilého balení IC založeného na TSV ve formátu 2.5D a 3D.

- Hybridní bondingové techniky: Hybridní bonding, který kombinuje přímé měděné bonding s bondingem dielektrického s dielektrickým, získává na popularitě jako metod pro dosažení ultra-jemných propojení a zlepšených elektrických vlastností. Tato technologie umožňuje balení s roztečí pod 10 mikronů, což je nezbytné pro integraci logiky a paměti nové generace. Amkor Technology a Intel Corporation oznámily významné investice do hybridního bondingu pro paměťové i logické zařízení.

- Heterogenní integrace: Trend integrace různorodých čipletů—jako jsou logické, paměťové, RF a analogové—v rámci jedné vrstvené skříně se zrychluje. Tento přístup umožňuje optimalizované výrobní uzly pro každou funkci, zlepšující celkový výkon systému a energetickou účinnost. Průmyslová asociace SEMI zdůrazňuje heterogenní integraci jako klíčový faktor pro pokročilé automobilové, 5G a řešení edge computing.

- Inovace v řízení tepla: Jak se zvyšuje hustota výkonu v důsledku vrstvení čipů, vyvíjejí se pokročilé tepelné rozhraní materiálů (TIM), mikrofluidní chlazení a integrované rozvodné systémy na teplo pro řízení odvodu tepla. Yole Group uvádí, že efektivní řízení tepla je nyní primárním diferenciátorem v návrhu balení s vrstvenými čipy, zejména na trhu s datovými centry a akcelerátory AI.

- Automatizované testování a inspekce: Složitost sestav s vrstvenými čipy vyžaduje pokročilé testovací a inspekční řešení, včetně vysoce rozlišeného rentgenového a AI-poháněného detekování vad. KLA Corporation a Teradyne rozšiřují svou nabídku, aby čelily unikátním výzvám spolehlivosti balení složeného z více čipů a výtěžnosti.

Tyto technologické trendy kolektivně posouvají trh balení mikroelektroniky s vrstvenými čipy směrem k větší integraci, výkonu a spolehlivosti, což jej umisťuje jako kritického usnadňovatele pro systémy elektroniky příští generace v roce 2025 a dál.

Konkurenční situace a vedoucí hráči

Konkurenční situace trhu balení mikroelektroniky s vrstvenými čipy v roce 2025 je charakterizována intenzivní inovací, strategickými partnerstvími a zaměřením na pokročilé výrobní kapacity. Tento sektor je poháněn poptávkou po vyšším výkonu zařízení, miniaturizaci a integraci v aplikacích jako jsou chytré telefony, vysoce výkonný computing, automobilová elektronika a zařízení IoT. Klíčoví hráči využívají své odbornosti v balení na úrovni waferu, technologii přesilových via (TSV) a heterogenní integraci, aby si udrželi konkurenční výhodu.

V čele trhu stojí zavedení poskytovatelé služeb balení a montáže polovodičů, včetně Amkor Technology, ASE Technology Holding a TSMC. Tyto společnosti učinily významné investice do R&D a výrobních kapacit na podporu výroby s vysokým objemem řešení s vrstvenými čipy. Například pokročilé technologie CoWoS (Chip-on-Wafer-on-Substrate) a SoIC (System on Integrated Chips) společnosti TSMC se široce adoptují pro vysoce výkonný computing a aplikace AI, zatímco Amkor Technology a ASE Technology Holding nabízejí široké portfolio služeb balení 2.5D a 3D pro spotřebitelský a podnikový trh.

IDM (integrated device manufacturers) jako Intel Corporation a Samsung Electronics jsou také významní, integrují balení s vrstvenými čipy do svých produktových roadmap, aby zvýšili výkon čipů a energetickou účinnost. Technologie Foveros společnosti Intel a platforma X-Cube společnosti Samsung představují proprietární přístupy k vertikální integraci a architekturám založeným na čipletech.

Nově vznikající hráči a specialisté v oblasti více čipů, včetně JCET Group a Powertech Technology Inc., získávají popularitu nabídkou přizpůsobených řešení a cílením na specifické vertikály, jako jsou automobilové a průmyslové elektroniky. Tyto společnosti často spolupracují s fabless výrobci polovodičů a systémovými integrátory, aby dodávaly na míru šitá balení s vrstvenými čipy.

Konkurenční prostředí je dále formováno probíhajícími fúzemi a akvizicemi, licencováním technologií a společnými podniky, neboť společnosti usilují o rozšíření svých schopností a globálního dosahu. Podle Yole Group se očekává, že trh bude i nadále vidět konsolidaci, přičemž přední hráči investují do propojení nové generace, pokročilých materiálů a automatizace, aby splnili vyvíjející se potřeby trhů AI, 5G a edge computing.

Předpovědi růstu trhu (2025–2030): CAGR, analýza příjmů a objemu

Trh balení mikroelektroniky s vrstvenými čipy je připraven na silný růst mezi lety 2025 a 2030, poháněný rostoucí poptávkou po vysoce výkonných, miniaturizovaných elektronických zařízení napříč sektorů spotřební elektroniky, automobilového průmyslu a datových center. Podle projekcí společnosti MarketsandMarkets se očekává, že globální trh 3D IC a balení s vrstvenými čipy zaznamená složenou roční míru růstu (CAGR) přibližně 12 % během tohoto období. Tato trajektorie růstu je podložena rostoucím přijetím pokročilých balicích řešení, aby se vyřešily omezení tradičních 2D architektur, zejména pokud jde o energetickou účinnost, rozměr a šířku pásma.

Odhady příjmů naznačují, že segment balení mikroelektroniky s vrstvenými čipy překročí 15 miliard USD do roku 2030, ve srovnání s přibližně 8,5 miliardy USD v roce 2025. Tento nárůst je přičítán proliferaci umělé inteligence (AI), infrastruktury 5G a edge computingu, z nichž všechny vyžadují vyšší hustotu propojení a zlepšené řízení tepla—klíčové výhody nabízené architekturami s vrstvenými čipy. Gartner zdůrazňuje, že posun polovodičového průmyslu směrem k heterogenní integraci a řešením systémů v balení (SiP) dále urychlí přijetí technologií balení s vrstvenými čipy.

Pokud jde o objem, počet dodaných jednotek s vrstvenými čipy se očekává, že poroste s CAGR 13–14 % od roku 2025 do roku 2030, což odráží jak zvýšené pronikání do vysoce objemových spotřebitelských zařízení, tak i expandující použití v automobilové elektronice a průmyslovém IoT. Yole Group uvádí, že přední tržiště a OSAT (outsourcovaná montáž polovodičů a testování) zvyšují investice do pokročilých balících linek, aby splnily tuto očekávanou poptávku, přičemž Asie a Tichomoří zůstává dominantním výrobním uzlem díky svému zavedenému ekosystému výroby polovodičů.

- CAGR (2025–2030): 12–14%

- Příjmy (2030): 15+ miliard USD

- Růst objemu: Řízený spotřební elektronikou, automobilovým průmyslem a datovými centry

- Klíčové regiony: Asie a Tichomoří vede, následovaná Severní Amerikou a Evropou

Celkově je trh balení mikroelektroniky s vrstvenými čipy nastaven na významnou expanzi, poháněnou technologickými inovacemi a neúprosně rostoucím tlakem na vyšší výkon a integraci v systémech elektroniky nové generace.

Regionální analýza trhu: Severní Amerika, Evropa, Asie a Tichomoří a zbytek světa

Globální trh balení mikroelektroniky s vrstvenými čipy zažívá dynamický růst, přičemž regionální trendy jsou formovány technologickými inovacemi, poptávkou koncových uživatelů a vývojem dodavatelského řetězce. V roce 2025 každá z regionů Severní Amerika, Evropa, Asie a Tichomoří a zbytek světa (RoW) prezentuje odlišné tržní charakteristiky a růstové faktory.

- Severní Amerika: Severní americký trh je podpořen silnými investicemi do pokročilé výroby polovodičů a silnou přítomností předních technologických firem. Tato oblast těží z významných aktivit výzkumu a vývoje, zejména ve Spojených státech, kde je tlak na domácí výrobu čipů podporován vládními iniciativami, jako je zákon CHIPS. Klíčovými aplikacemi jsou vysoce výkonný computing, automobilová elektronika a obranné systémy. Podle Semiconductor Industry Association se očekává, že Severní Amerika udrží stabilní růst v balení s vrstvenými čipy, poháněn poptávkou po miniaturizovaných, vysokohustotních řešeních v AI a infrastruktuře 5G.

- Evropa: Evropský trh je charakterizován zaměřením na automobilové, průmyslovou automatizaci a aplikace IoT. Důraz regionu na kvalitu a spolehlivost, spolu se přísnými regulačními standardy, podporuje přijetí pokročilých balicích technologií. Iniciativy jako Evropský chipský zákon mají za cíl posílit místní polovodičové kapacity. Podle SEMI evropští výrobci stále více investují do řešení s vrstvenými čipy, aby podpořili rostoucí sektory elektrických vozidel a chybré výroby v regionu.

- Asie a Tichomoří: Asie a Tichomoří dominuje globálnímu trhu balení mikroelektroniky s vrstvenými čipy, přičemž v roce 2025 představuje největší podíl. Toto vedení je podloženo přítomností hlavních tržišť a poskytovatelů OSAT (outsourcovaná montáž polovodičů a testování) v zemích jako Tchaj-wan, Jižní Korea, Čína a Japonsko. Rychlé přijetí spotřební elektroniky, chytrých telefonů a datových center v regionu zvyšuje poptávku po balení s vysokou hustotou. Podle IC Insights je růst trhu v oblasti Asie a Tichomoří dále urychlován vládními dotacemi a agresivním rozšiřováním kapacity předních hráčů.

- Zbytek světa (RoW): Segment RoW, včetně Latinské Ameriky, Blízkého východu a Afriky, zůstává v počátcích, ale vykazuje potenciál pro růst, jak se rozšiřují iniciativy digitální transformace. Investice do telekomunikační infrastruktury a vznikající výrobní uzly elektroniky by měly postupně zvýšit poptávku po řešeních balení s vrstvenými čipy, jak uvedl Gartner.

Celkově regionální dynamika v roce 2025 odráží konvergenci inovací, politické podpory a poptávky ve finálních trzích, přičemž Asie a Tichomoří vedou v objemu a Severní Amerika a Evropa se zaměřují na aplikace o vysoké hodnotě a specializace.

Budoucí vyhlídky: Nově vznikající aplikace a investiční hotspoty

Budoucí vyhlídky pro balení mikroelektroniky s vrstvenými čipy v roce 2025 jsou formovány rychlými pokroky v integraci polovodičů, proliferací AI a vysoce výkonným computingem, a rostoucí poptávkou po miniaturizovaných, vysokohustotních elektronických systémech. Balení s vrstvenými čipy, které zahrnuje vertikální integraci více polovodičových čipů v jedné skříni, je stále více uznáváno jako klíčový usnadňovatel pro zařízení nové generace napříč několika sektory s vysokým růstem.

Nově vznikající aplikace jsou obzvláště výrazné v datových centrech, infrastruktuře 5G a edge computingu. Potřeba vyšší šířky pásma a nižší latence v těchto prostředích pohání přijetí topologie balení s 2.5D a 3D vrstvenými čipy, které nabízejí zlepšený elektrický výkon a zkrácené délky propojení. V roce 2025 se očekává, že integrace paměti s vysokou šířkou pásma (HBM) s logickými čipy zrychlí, aby podpořila výpočetní nároky akcelerátorů AI a pokročilých grafických procesorů. Společnosti jako Samsung Electronics a TSMC investují značné prostředky do pokročilých balicích linek, aby uspokojily tuto poptávku.

Další nově vznikající aplikací je automobilový průmysl, kde balení s vrstvenými čipy umožňuje vývoj kompaktních, vysoce spolehlivých modulů pro pokročilé systémy asistence řidičů (ADAS) a autonomní vozidla. Přísné požadavky automobilového průmyslu na řízení tepla a spolehlivost posouvají inovace v technologiích TSV a balení na úrovni waferu, přičemž dodavatelé jako Infineon Technologies a NXP Semiconductors rozšiřují své portfolia, aby vyhovovaly těmto potřebám.

Investiční hotspoty v roce 2025 se očekává, že budou soustředěny v Asii a Tichomoří, zejména na Tchaj-wanu, v Jižní Koreji a Číně, kde vládní pobídky a robustní ekosystémy tržišť urychlují R&D a expanze kapacity. Podle Gartneru se očekává, že globální trh pokročilého balení poroste s CAGR přes 7 % až do roku 2025, přičemž řešení s vrstvenými čipy představují významný podíl tohoto růstu. Venture kapitál a strategické investice také plynou do startupů vyvíjejících nové materiály pro propojení a techniky heterogenní integrace, jak zdůraznil nedávný sledovaný financovaný cyklus společnosti CB Insights.

- AI a HPC: Balení s vrstvenými čipy pro akcelerátory AI a GPU

- Automotiv: Vysoká spolehlivost, kompaktní moduly pro ADAS a EV

- 5G/Edge: Řešení s nízkou latencí a vysokou šířkou pásma pro síťovou infrastrukturu

- Asie a Tichomoří: Vede v investicích a expanzích výroby

Stručně řečeno, rok 2025 přinese balení mikroelektroniky s vrstvenými čipy do popředí inovací polovodičů, s výrazným momentum v AI, automobilovém a komunikačním sektoru a významnými investičními aktivitami v Asii a startupech zaměřených na pokročilé materiály.

Výzvy, rizika a strategické příležitosti

Balení mikroelektroniky s vrstvenými čipy, základní prvek pokročilé integrace polovodičů, čelí v roce 2025 složitému spektru výzev a rizik, ale také představuje významné strategické příležitosti pro hráče v průmyslu. Hlavní technickou výzvou zůstává řízení tepla. Jak se více čipů integruje vertikálně, zajištění odvodu tepla se stává čím dál obtížnější, což ohrožuje spolehlivost a výkon zařízení. Pokročilé materiály pro tepelné rozhraní a inovativní designy zdrojových rozvodů se zkoumají, ale jejich integrace přidává náklady a složitost do výrobního procesu (SEMI).

Rizika výtěžnosti a spolehlivosti jsou v architekturách s vrstvenými čipy také zvýšena. Zvýšený počet propojení, jako je přesilové via (TSV), zvyšuje pravděpodobnost vad, které ovlivňují celkové výtěžnosti. Dále heterogenní integrace—kombinování čipů z různých výrobních uzlů nebo tržišť—představuje výzvy pro kompatibilitu a testování. Potřeba pokročilých inspekčních a metrologických nástrojů roste, ale tato řešení mohou výrazně zvýšit kapitálové výdaje (TechInsights).

Komplexita dodavatelského řetězce je dalším kritickým rizikem. Balení s vrstvenými čipy často vyžaduje spolupráci napříč několika dodavateli pro wafery, substráty a montážní služby. Přerušení v jakémkoli segmentu může zdržet výrobu a zvýšit náklady. Geopolitické napětí a exportní kontroly, zejména v technologickém obchodě mezi USA a Čínou, dále zhoršují zranitelnosti dodavatelského řetězce (Gartner).

Navzdory těmto výzvám jsou přítomny strategické příležitosti. Poptávka po vysoce výkonném computingu, akcelerátorech AI a pokročilých mobilních zařízeních pohání rychlé přijetí řešení s vrstvenými čipy. Společnosti, které investují do proprietárního řízení tepla, pokročilého testování a robustních strategií dodavatelského řetězce, se mohou diferencovat a zachytit prémiové segmenty trhu. Kromě toho partnerství mezi tržišti, OSAT a dodavateli EDA (Electronic Design Automation) umožňuje nové designové a výrobní paradigmata, jako jsou architektury založené na čipletech, které mohou dále uvolnit hodnotu (TSMC).

- Řízení tepla a spolehlivost zůstávají hlavními technickými překážkami.

- Ztráty výtěžnosti a náklady na inspekci rostou s rostoucí složitostí integrace.

- Rizika dodavatelského řetězce jsou zvýšena geopolitickými a logistickými faktory.

- Strategické investice do R&D, partnerství a odolnosti dodavatelského řetězce nabízí konkurenční výhody.

Zdroje a odkazy

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights