Informe del Mercado de Empaques de Microelectrónica con Chips Apilados 2025: Crecimiento, Cambios Tecnológicos y Perspectivas Estratégicas para los Próximos 5 Años. Explora Tendencias Clave, Pronósticos y Dinámicas Competitivas que Moldean la Industria.

- Resumen Ejecutivo y Visión General del Mercado

- Tendencias Tecnológicas Clave en el Empaque de Microelectrónica con Chips Apilados

- Paisaje Competitivo y Principales Actores

- Pronósticos de Crecimiento del Mercado (2025–2030): CAGR, Análisis de Ingresos y Volumen

- Análisis del Mercado Regional: América del Norte, Europa, Asia-Pacífico y Resto del Mundo

- Perspectivas Futuras: Aplicaciones Emergentes y Puntos Calientes de Inversión

- Desafíos, Riesgos y Oportunidades Estratégicas

- Fuentes y Referencias

Resumen Ejecutivo y Visión General del Mercado

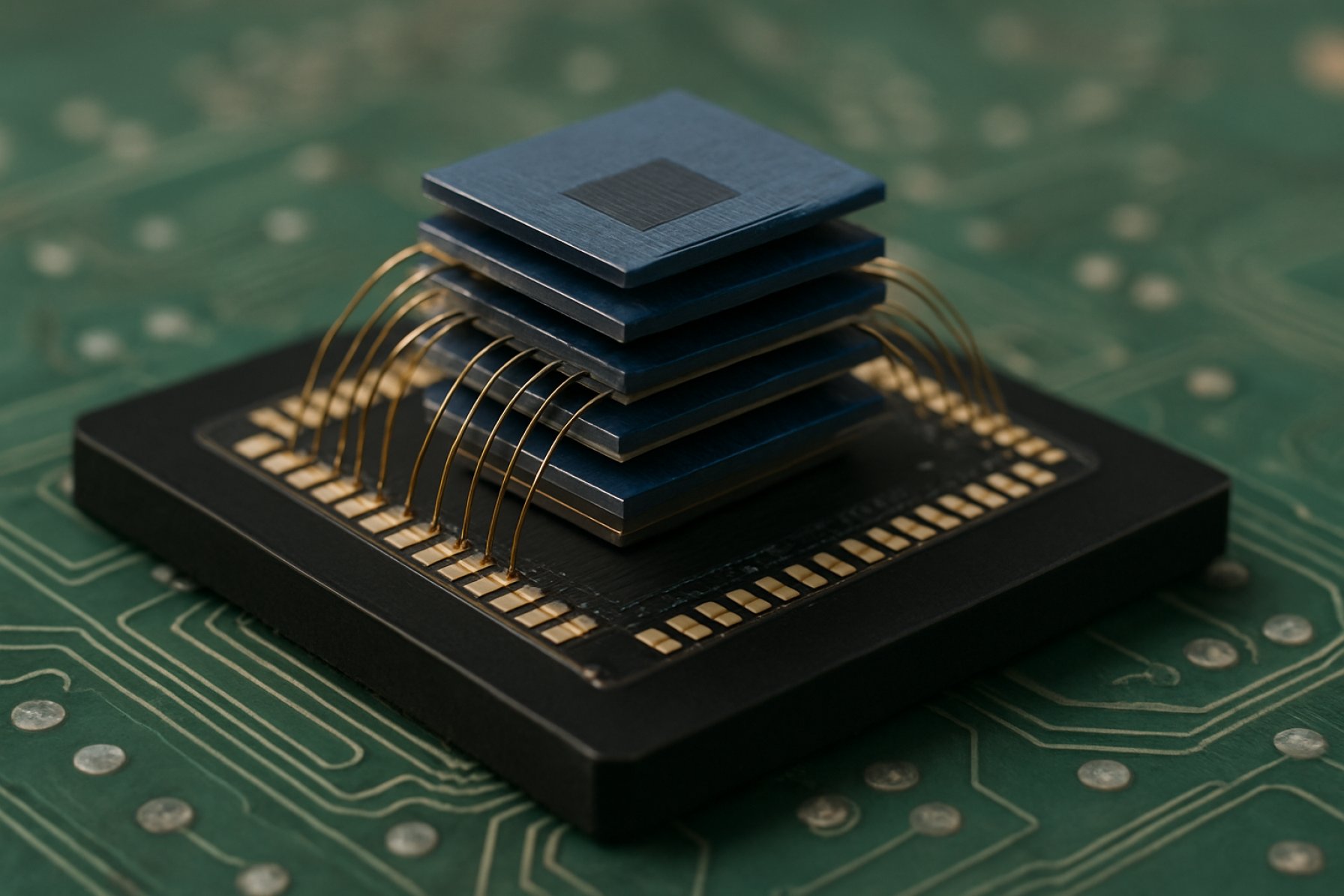

El empaque de microelectrónica con chips apilados se refiere a la integración de múltiples chips semiconductores dentro de un solo paquete, organizados verticalmente para optimizar el espacio, el rendimiento y la funcionalidad. Esta tecnología de empaque avanzada es fundamental para satisfacer las crecientes demandas de miniaturización, mayor rendimiento y eficiencia energética en sectores como la electrónica de consumo, automotriz, telecomunicaciones y centros de datos. A partir de 2025, el mercado global de empaques de microelectrónica con chips apilados experimenta un sólido crecimiento, impulsado por la proliferación de dispositivos 5G, aplicaciones de inteligencia artificial (IA) y el Internet de las Cosas (IoT).

Según Gartner, se proyecta que el mercado de empaques con chips apilados logre una tasa de crecimiento anual compuesta (CAGR) de más del 8% entre 2023 y 2027, con ingresos que se espera superen los 12 mil millones de dólares para 2025. Este crecimiento se basa en la creciente adopción de circuitos integrados 3D (3D ICs), soluciones de sistema-en-paquete (SiP) y módulos de memoria de alto ancho de banda (HBM), todos los cuales aprovechan arquitecturas de chips apilados para ofrecer un rendimiento mejorado y una reducción en factores de forma.

Actores clave de la industria como TSMC, Samsung Electronics e Intel Corporation están invirtiendo fuertemente en investigación y desarrollo para avanzar en las tecnologías de vía de silicio a través (TSV) y empaque a nivel de oblea (WLP). Estas innovaciones permiten tener una mayor densidad de interconexión, mejor gestión térmica y menor consumo de energía, que son críticos para aplicaciones de próxima generación en aceleradores de IA, sistemas avanzados de asistencia al conductor (ADAS) y computación de alto rendimiento (HPC).

Regionalmente, Asia-Pacífico domina el mercado de empaques con chips apilados, representando más del 60% de la capacidad de producción global, principalmente debido a la presencia de fundiciones líderes y proveedores de OSAT (ensamblaje y prueba de semiconductores externalizados) en países como Taiwán, Corea del Sur y China. América del Norte y Europa también están presenciando un aumento en la adopción, particularmente en la electrónica automotriz y la infraestructura de centros de datos, como señalaba IC Insights.

En resumen, el empaque de microelectrónica con chips apilados es una tecnología fundamental para la evolución de la industria de semiconductores en 2025, permitiendo una mayor integración, rendimiento y eficiencia en una amplia gama de aplicaciones. La trayectoria del mercado está moldeada por avances tecnológicos continuos, inversiones estratégicas por parte de los principales actores y la demanda constante de sistemas electrónicos más inteligentes, pequeños y potentes.

Tendencias Tecnológicas Clave en el Empaque de Microelectrónica con Chips Apilados

El empaque de microelectrónica con chips apilados está a la vanguardia de la innovación en semiconductores, permitiendo un mayor rendimiento de los dispositivos, funcionalidad aumentada y reducción en factores de forma mediante la integración vertical de múltiples chips semiconductores dentro de un solo paquete. A medida que la industria avanza hacia 2025, varias tendencias tecnológicas clave están moldeando la evolución y adopción de soluciones de empaque con chips apilados.

- Integración Avanzada de Vías de Silicio a Través (TSV): La tecnología TSV sigue siendo un pilar para el apilamiento de chips de alta densidad, ofreciendo interconexiones de alta velocidad y bajo retardo entre chips alineados verticalmente. En 2025, los fabricantes están refinando los procesos de TSV para reducir el diámetro y el espaciamiento de las vías, aumentando así la densidad de interconexión y mejorando el rendimiento eléctrico. Esto es especialmente crítico para aplicaciones de computación de alto rendimiento (HPC) y de inteligencia artificial (IA), donde el ancho de banda de memoria es un cuello de botella. TSMC y Samsung Electronics lideran la carga en la comercialización de empaques de circuitos integrados 2.5D y 3D basados en TSV.

- Técnicas de Unión Híbrida: La unión híbrida, que combina la unión directa de cobre a cobre y de dieléctrico a dieléctrico, está ganando terreno como un método para lograr interconexiones de espaciamiento ultra-fino y características eléctricas mejoradas. Esta tecnología permite el apilamiento con espaciamiento inferior a 10 micrones, que es esencial para la integración lógica-memoria de próxima generación. Amkor Technology e Intel Corporation han anunciado inversiones significativas en unión híbrida para dispositivos de memoria y lógica.

- Integración Heterogénea: La tendencia hacia la integración de diversos chips, como lógica, memoria, RF y analógico, dentro de un solo paquete apilado se está acelerando. Este enfoque permite nodos de proceso optimizados para cada función, mejorando el rendimiento y la eficiencia general del sistema. La asociación de la industria SEMI destaca la integración heterogénea como un habilitador clave para soluciones automotrices avanzadas, 5G y computación en el borde.

- Innovaciones en Gestión Térmica: A medida que el apilamiento de chips aumenta la densidad de potencia, se están desarrollando materiales avanzados para interfaces térmicas (TIMs), refrigeración microfluídica y dispersores de calor integrados para gestionar la disipación de calor. Yole Group informa que la gestión térmica efectiva es ahora un diferenciador primario en el diseño de paquetes de chips apilados, especialmente para los mercados de centros de datos y aceleradores de IA.

- Pruebas e Inspección Automatizadas: La complejidad de los ensamblajes de chips apilados exige soluciones avanzadas de prueba e inspección, incluidos rayos X de alta resolución y detección de defectos impulsada por IA. KLA Corporation y Teradyne están expandiendo sus ofertas para abordar los desafíos únicos de la fiabilidad y el rendimiento de los paquetes de múltiples chips.

Estas tendencias tecnológicas están impulsando colectivamente el mercado de empaques de microelectrónica con chips apilados hacia una mayor integración, rendimiento y fiabilidad, posicionándolo como un habilitador crítico para sistemas electrónicos de próxima generación en 2025 y más allá.

Paisaje Competitivo y Principales Actores

El paisaje competitivo del mercado de empaques de microelectrónica con chips apilados en 2025 se caracteriza por una intensa innovación, asociaciones estratégicas y un enfoque en capacidades avanzadas de fabricación. Este sector está impulsado por la demanda de un mayor rendimiento de los dispositivos, miniaturización e integración en aplicaciones como teléfonos inteligentes, computación de alto rendimiento, electrónica automotriz y dispositivos IoT. Los actores clave están aprovechando su experiencia en empaque a nivel de oblea, tecnología de vías de silicio a través (TSV) e integración heterogénea para mantener una ventaja competitiva.

Lideran el mercado los proveedores de servicios de empaque y ensamblaje de semiconductores establecidos, incluidos Amkor Technology, ASE Technology Holding y TSMC. Estas empresas han realizado inversiones significativas en I+D y capacidad de producción para respaldar la fabricación a gran escala de soluciones con chips apilados. Por ejemplo, las innovadoras tecnologías CoWoS (Chip-on-Wafer-on-Substrate) y SoIC (System on Integrated Chips) de TSMC son ampliamente adoptadas para aplicaciones de computación de alta gama y IA, mientras que Amkor Technology y ASE Technology Holding ofrecen un amplio portafolio de servicios de empaque 2.5D y 3D para mercados de consumo y corporativos.

Los IDM (Manufacturadores de Dispositivos Integrados) como Intel Corporation y Samsung Electronics también son prominentes, integrando el empaque con chips apilados en sus hojas de ruta de productos para mejorar el rendimiento del chip y la eficiencia energética. La tecnología Foveros de Intel y la plataforma X-Cube de Samsung ejemplifican enfoques propios para la integración vertical y arquitecturas basadas en chiplets.

Actores emergentes y especialistas de nicho, incluidos JCET Group y Powertech Technology Inc., están ganando terreno al ofrecer soluciones personalizadas y enfocarse en verticales específicos como la electrónica automotriz e industrial. Estas empresas a menudo colaboran con firmas de semiconductores sin fábrica y con integradores de sistemas para ofrecer paquetes de chips apilados a medida.

El entorno competitivo se ve además moldeado por actividades de fusiones y adquisiciones en curso, licencias de tecnología y empresas conjuntas, a medida que las compañías buscan expandir sus capacidades y alcance global. Según Yole Group, se espera que el mercado continúe con la concentración, con los principales actores invirtiendo en interconexiones de próxima generación, materiales avanzados y automatización para abordar las necesidades evolutivas de los mercados de IA, 5G y computación en el borde.

Pronósticos de Crecimiento del Mercado (2025–2030): CAGR, Análisis de Ingresos y Volumen

El mercado de empaques de microelectrónica con chips apilados está preparado para un crecimiento robusto entre 2025 y 2030, impulsado por la creciente demanda de dispositivos electrónicos miniaturizados y de alto rendimiento en aplicaciones de electrónica de consumo, automotriz y centros de datos. Según proyecciones de MarketsandMarkets, se espera que el mercado global de 3D IC y empaques con chips apilados registre una tasa de crecimiento anual compuesta (CAGR) de aproximadamente el 12% durante este periodo. Esta trayectoria de crecimiento se basa en la creciente adopción de soluciones de empaque avanzadas para abordar las limitaciones de las arquitecturas 2D tradicionales, particularmente en términos de eficiencia energética, factor de forma y ancho de banda.

Las proyecciones de ingresos indican que el segmento de empaques de microelectrónica con chips apilados superará los 15 mil millones de dólares para 2030, en comparación con un estimado de 8.5 mil millones de dólares en 2025. Este aumento se atribuye a la proliferación de la inteligencia artificial (IA), la infraestructura 5G y la computación en el borde, todos los cuales requieren una mayor densidad de interconexión y una mejor gestión térmica, ventajas clave que ofrecen las arquitecturas de chips apilados. Gartner destaca que el cambio de la industria de semiconductores hacia la integración heterogénea y las soluciones de sistema-en-paquete (SiP) acelerará aún más la adopción de tecnologías de empaque con chips apilados.

En términos de volumen, se proyecta que el número de unidades de chips apilados enviadas crecerá a una tasa compuesta anual (CAGR) del 13 al 14% de 2025 a 2030, reflejando tanto un aumento en la penetración en dispositivos de consumo de alto volumen como un uso en expansión en la electrónica automotriz y el IoT industrial. Yole Group informa que las principales fundiciones y OSAT (proveedores de ensamblaje y prueba de semiconductores externalizados) están aumentando sus inversiones en líneas de empaque avanzadas para satisfacer esta demanda anticipada, con Asia-Pacífico continuando siendo el centro de producción dominante debido a su ecosistema de fabricación de semiconductores establecido.

- CAGR (2025–2030): 12–14%

- Ingresos (2030): Más de 15 mil millones de USD

- Crecimiento del Volumen: Impulsado por electrónica de consumo, automotriz y aplicaciones de centros de datos

- Regiones Clave: Asia-Pacífico lidera, seguido de América del Norte y Europa

En general, el mercado de empaques de microelectrónica con chips apilados está listo para una expansión significativa, impulsada por la innovación tecnológica y el impulso constante por un mayor rendimiento e integración en los sistemas electrónicos de próxima generación.

Análisis del Mercado Regional: América del Norte, Europa, Asia-Pacífico y Resto del Mundo

El mercado global de empaques de microelectrónica con chips apilados está experimentando un crecimiento dinámico, con tendencias regionales moldeadas por la innovación tecnológica, la demanda de los usuarios finales y los desarrollos de la cadena de suministro. En 2025, América del Norte, Europa, Asia-Pacífico y el Resto del Mundo (RoW) presentan características de mercado y motores de crecimiento distintos.

- América del Norte: El mercado norteamericano está impulsado por inversiones sólidas en fabricación avanzada de semiconductores y una fuerte presencia de empresas tecnológicas líderes. La región se beneficia de importantes actividades de I+D, particularmente en los Estados Unidos, donde el impulso por la producción local de chips está respaldado por iniciativas gubernamentales como la Ley CHIPS. Las aplicaciones clave incluyen computación de alto rendimiento, electrónica automotriz y sistemas de defensa. Según la Asociación de la Industria de Semiconductores, se espera que América del Norte mantenga un crecimiento constante en el empaque con chips apilados, impulsado por la demanda de soluciones miniaturizadas y de alta densidad en infraestructura de IA y 5G.

- Europa: El mercado europeo se caracteriza por un enfoque en aplicaciones automotrices, automatización industrial e IoT. El énfasis de la región en la calidad y fiabilidad, junto con estándares regulatorios estrictos, fomenta la adopción de tecnologías de empaque avanzadas. Iniciativas como la Ley Europea de Chips buscan fortalecer las capacidades locales de semiconductores. Según SEMI, los fabricantes europeos están invirtiendo en soluciones de chips apilados para apoyar los sectores en crecimiento de vehículos eléctricos y manufactura inteligente de la región.

- Asia-Pacífico: Asia-Pacífico domina el mercado global de empaques de microelectrónica con chips apilados, representando la mayor participación en 2025. Este liderazgo está respaldado por la presencia de importantes fundiciones y proveedores de OSAT en países como Taiwán, Corea del Sur, China y Japón. La rápida adopción de electrónica de consumo, teléfonos inteligentes y centros de datos en la región alimenta la demanda de empaque de alta densidad. Según IC Insights, el crecimiento del mercado de Asia-Pacífico se ve acelerado por incentivos gubernamentales y expansiones agresivas de capacidad por parte de los actores líderes.

- Resto del Mundo (RoW): El segmento de RoW, incluida América Latina, Medio Oriente y África, sigue siendo incipiente pero muestra potencial de crecimiento a medida que se expanden las iniciativas de transformación digital. Las inversiones en infraestructura de telecomunicaciones y emergentes centros de fabricación de electrónica se espera que aumenten gradualmente la demanda de soluciones de empaque con chips apilados, como lo señala Gartner.

En general, las dinámicas regionales en 2025 reflejan una convergencia de innovación, apoyo político y demanda de los mercados finales, con Asia-Pacífico liderando en volumen y América del Norte y Europa enfocándose en aplicaciones especializadas de alto valor.

Perspectivas Futuras: Aplicaciones Emergentes y Puntos Calientes de Inversión

Las perspectivas futuras para el empaque de microelectrónica con chips apilados en 2025 están moldeadas por avances rápidos en la integración de semiconductores, la proliferación de IA y computación de alto rendimiento, y la creciente demanda de sistemas electrónicos miniaturizados y de alta densidad. El empaque con chips apilados, que involucra la integración vertical de múltiples chips semiconductores dentro de un solo paquete, es cada vez más reconocido como un habilitador clave para dispositivos de próxima generación en varios sectores de alto crecimiento.

Las aplicaciones emergentes son particularmente prominentes en centros de datos, infraestructura 5G y computación en el borde. La necesidad de mayor ancho de banda y menor latencia en estos entornos está impulsando la adopción de arquitecturas de chips apilados 2.5D y 3D, que ofrecen un mejor rendimiento eléctrico y menores longitudes de interconexión. En 2025, se espera que la integración de memoria de alto ancho de banda (HBM) con chips lógicos se acelere, apoyando las demandas computacionales de aceleradores de IA y procesadores gráficos avanzados. Empresas como Samsung Electronics y TSMC están invirtiendo fuertemente en líneas de empaque avanzadas para satisfacer esta demanda.

Otra aplicación emergente se encuentra en el sector automotriz, donde el empaque con chips apilados está permitiendo el desarrollo de módulos compactos de alta fiabilidad para sistemas avanzados de asistencia al conductor (ADAS) y vehículos autónomos. Los estrictos requisitos de la industria automotriz para la gestión térmica y la fiabilidad están impulsando la innovación en tecnologías de vía de silicio a través (TSV) y empaque a nivel de oblea, con proveedores como Infineon Technologies y NXP Semiconductors expandiendo sus carteras para abordar estas necesidades.

Se espera que los puntos calientes de inversión en 2025 se centren en Asia-Pacífico, particularmente en Taiwán, Corea del Sur y China, donde incentivos gubernamentales y ecosistemas de fundición robustos están acelerando I+D y expansión de capacidad. Según Gartner, se proyecta que el mercado global de empaque avanzado crecerá a una tasa compuesta anual (CAGR) de más del 7% hasta 2025, con soluciones de chips apilados representando una parte significativa de este crecimiento. Capital de riesgo e inversiones estratégicas también están fluyendo hacia startups que desarrollan nuevos materiales de interconexión y técnicas de integración heterogénea, como lo destacan las rondas de financiamiento recientes rastreadas por CB Insights.

- IA y HPC: Empaque de chips apilados para aceleradores de IA y GPU

- Automotriz: Módulos compactos de alta fiabilidad para ADAS y vehículos eléctricos

- 5G/Edge: Soluciones de baja latencia y alto ancho de banda para infraestructura de red

- Asia-Pacífico: Región líder en inversión y expansión de fabricación

En resumen, 2025 verá el empaque de microelectrónica con chips apilados a la vanguardia de la innovación en semiconductores, con un fuerte impulso en IA, automotriz y comunicaciones, y una actividad de inversión significativa en Asia-Pacífico y startups de materiales avanzados.

Desafíos, Riesgos y Oportunidades Estratégicas

El empaque de microelectrónica con chips apilados, un pilar de la integración avanzada de semiconductores, enfrenta un paisaje complejo de desafíos y riesgos en 2025, pero también presenta oportunidades estratégicas significativas para los actores de la industria. El principal desafío técnico sigue siendo la gestión térmica. A medida que más chips se integran verticalmente, la disipación de calor se vuelve cada vez más problemática, poniendo en riesgo la fiabilidad y el rendimiento del dispositivo. Se están explorando materiales avanzados para interfaces térmicas y diseños innovadores de dispersores de calor, pero su integración agrega costos y complejidad al proceso de fabricación (SEMI).

Los riesgos de rendimiento y fiabilidad también están aumentados en arquitecturas de chips apilados. El mayor número de interconexiones, como las vías de silicio a través (TSV), incrementa la probabilidad de defectos, lo que impacta en el rendimiento global. Además, la integración heterogénea—combinando chips de diferentes nodos de proceso o fundiciones—introduce desafíos de compatibilidad y pruebas. La necesidad de herramientas avanzadas de inspección y metrología está creciendo, pero estas soluciones pueden aumentar significativamente el gasto de capital (TechInsights).

La complejidad de la cadena de suministro es otro riesgo crítico. El empaque con chips apilados a menudo requiere colaboración entre múltiples proveedores de obleas, sustratos y servicios de ensamblaje. Las interrupciones en cualquier segmento pueden retrasar la producción y aumentar costos. Las tensiones geopolíticas y los controles de exportación, particularmente en el comercio tecnológico entre Estados Unidos y China, agravan aún más las vulnerabilidades de la cadena de suministro (Gartner).

A pesar de estos desafíos, abundan las oportunidades estratégicas. La demanda de computación de alto rendimiento, aceleradores de IA y dispositivos móviles avanzados está impulsando la rápida adopción de soluciones de chips apilados. Las empresas que invierten en gestión térmica propia, pruebas avanzadas y estrategias robustas de cadena de suministro pueden diferenciarse y capturar segmentos de mercado premium. Además, las asociaciones entre fundiciones, OSAT (ensamblaje y prueba de semiconductores externalizados) y proveedores de EDA (Automatización del Diseño Electrónico) están habilitando nuevos paradigmas de diseño y fabricación, como arquitecturas basadas en chiplets, que pueden desbloquear aún más valor (TSMC).

- La gestión térmica y la fiabilidad siguen siendo los principales obstáculos técnicos.

- Las pérdidas de rendimiento y los costos de inspección están aumentando con la creciente complejidad de la integración.

- Los riesgos de la cadena de suministro se amplifican por factores geopolíticos y logísticos.

- Inversiones estratégicas en I&D, asociaciones y resiliencia de la cadena de suministro ofrecen ventajas competitivas.

Fuentes y Referencias

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Asociación de la Industria de Semiconductores

- Infineon Technologies

- NXP Semiconductors

- TechInsights