Rapport sur le marché de l’emballage de microélectronique à die empilé 2025 : Croissance, évolutions technologiques et informations stratégiques pour les 5 prochaines années. Explorez les principales tendances, prévisions et dynamiques concurrentielles qui façonneront l’industrie.

- Résumé Exécutif & Aperçu du Marché

- Principales Tendances Technologiques dans l’Emballage de Microélectronique à Die Empilé

- Paysage Concurrentiel et Acteurs Principaux

- Prévisions de Croissance du Marché (2025–2030) : TCAC, Analyse des Revenus et des Volumes

- Analyse du Marché Régional : Amérique du Nord, Europe, Asie-Pacifique et Reste du Monde

- Perspectives Futures : Applications Émergentes et Zones d’Investissement

- Défis, Risques et Opportunités Stratégiques

- Sources & Références

Résumé Exécutif & Aperçu du Marché

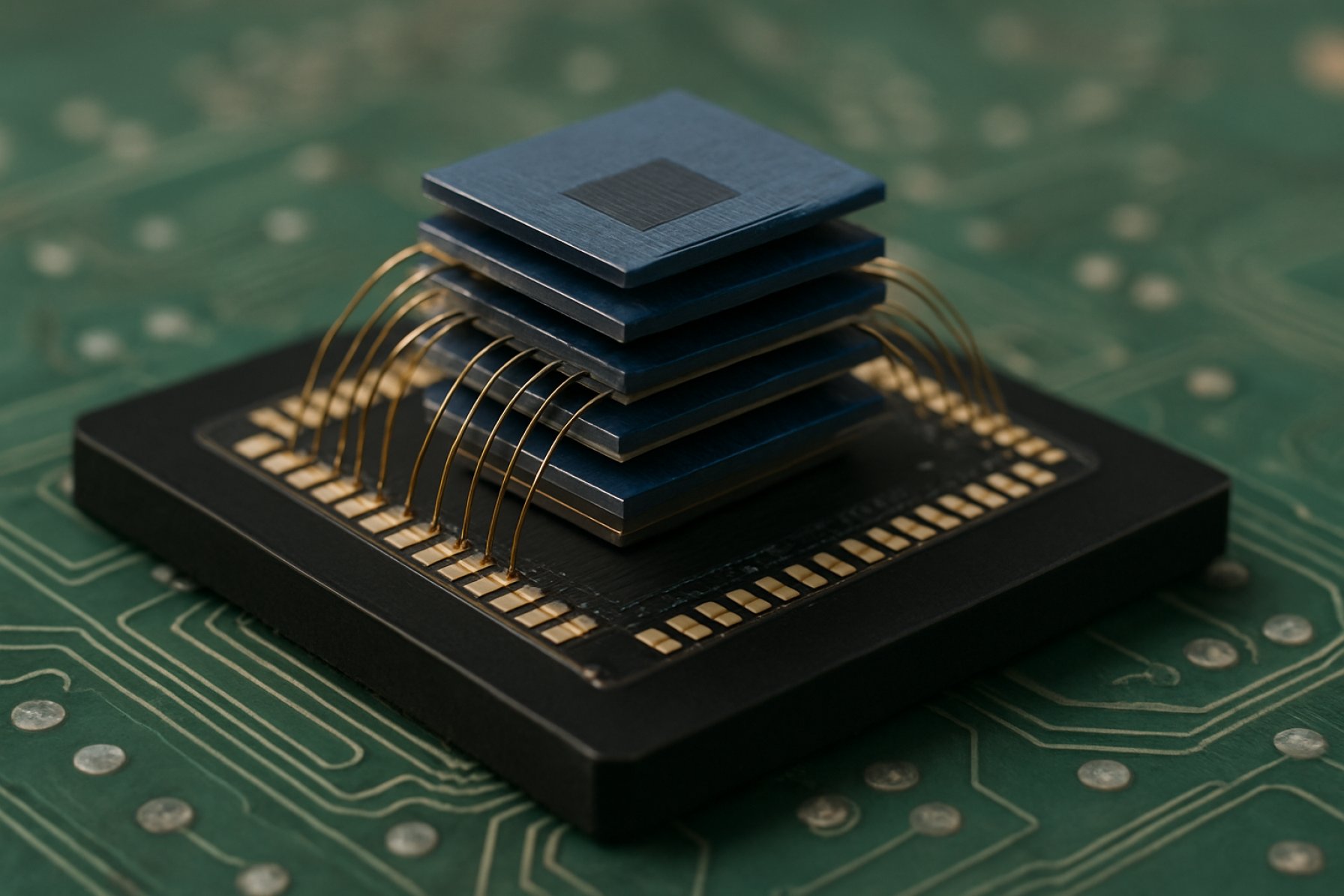

L’emballage de microélectronique à die empilé fait référence à l’intégration de plusieurs dies de semi-conducteurs au sein d’un seul emballage, disposés verticalement pour optimiser l’espace, la performance et la fonctionnalité. Cette technologie d’emballage avancée est essentielle pour répondre aux demandes croissantes de miniaturisation, de performance supérieure et d’efficacité énergétique dans des secteurs tels que l’électronique grand public, l’automobile, les télécommunications et les centres de données. En 2025, le marché mondial de l’emballage de microélectronique à die empilé connaît une forte croissance, soutenue par la prolifération des appareils 5G, des applications d’intelligence artificielle (IA) et de l’Internet des Objets (IoT).

Selon Gartner, le marché de l’emballage à die empilé devrait connaître un taux de croissance annuel composé (TCAC) de plus de 8 % entre 2023 et 2027, avec des revenus qui devraient dépasser 12 milliards de dollars d’ici 2025. Cette croissance est soutenue par l’adoption accrue des circuits intégrés 3D (3D IC), des solutions système-en-emballage (SiP) et des modules de mémoire à haut débit (HBM), tous tirant parti des architectures à die empilé pour offrir une performance améliorée et des facteurs de forme réduits.

Les principaux acteurs de l’industrie, tels que TSMC, Samsung Electronics et Intel Corporation, investissent massivement dans la recherche et le développement pour faire avancer les technologies via-silicium (TSV) et d’emballage au niveau des plaquettes (WLP). Ces innovations permettent des densités d’interconnexion plus élevées, une gestion thermique améliorée et une consommation d’énergie réduite, qui sont critiques pour les applications de prochaine génération dans les accélérateurs IA, les systèmes avancés d’assistance à la conduite (ADAS) et l’informatique haute performance (HPC).

Régionalement, l’Asie-Pacifique domine le marché de l’emballage à die empilé, représentant plus de 60 % de la capacité de production mondiale, principalement grâce à la présence de fonderies et de fournisseurs OSAT (assemblage et test de semi-conducteurs externalisés) dans des pays comme Taïwan, la Corée du Sud et la Chine. L’Amérique du Nord et l’Europe constatent également une adoption accrue, notamment dans l’électronique automobile et l’infrastructure des centres de données, comme l’indique IC Insights.

En résumé, l’emballage de microélectronique à die empilé est une technologie fondamentale pour l’évolution de l’industrie des semi-conducteurs en 2025, permettant une intégration, une performance et une efficacité supérieures dans un large éventail d’applications. La trajectoire du marché est façonnée par les progrès technologiques continus, les investissements stratégiques des principaux acteurs et la demande incessante pour des systèmes électroniques plus intelligents, plus petits et plus puissants.

Principales Tendances Technologiques dans l’Emballage de Microélectronique à Die Empilé

L’emballage de microélectronique à die empilé est à la pointe de l’innovation dans le secteur des semi-conducteurs, permettant une performance accrue des dispositifs, une fonctionnalité améliorée et des facteurs de forme réduits grâce à l’intégration verticale de plusieurs dies de semi-conducteurs au sein d’un seul emballage. À mesure que l’industrie avance vers 2025, plusieurs tendances technologiques clés façonnent l’évolution et l’adoption des solutions d’emballage à die empilé.

- Intégration Avancée via-Silicone (TSV) : La technologie TSV demeure une pierre angulaire de l’empilage de dies à haute densité, offrant des interconnexions à faible latence et à haut débit entre les dies alignés verticalement. En 2025, les fabricants perfectionnent les processus TSV pour réduire le diamètre et l’espacement des vias, augmentant ainsi la densité d’interconnexion et améliorant les performances électriques. Ceci est particulièrement critique pour l’informatique haute performance (HPC) et les applications d’intelligence artificielle (IA), où la bande passante de la mémoire est un goulot d’étranglement. TSMC et Samsung Electronics mènent la charge dans la commercialisation des emballages 2.5D et 3D basés sur TSV avancés.

- Techniques de Bonding Hybride : Le bonding hybride, qui combine le bonding direct cuivre à cuivre et diélectrique à diélectrique, est en train de gagner en traction comme méthode pour atteindre des interconnexions à pitch ultra-fin et des caractéristiques électriques améliorées. Cette technologie permet un empilage à pitch inférieur à 10 microns, ce qui est essentiel pour l’intégration logique-mémorie de prochaine génération. Amkor Technology et Intel Corporation ont annoncé des investissements significatifs dans le bonding hybride pour les dispositifs de mémoire et de logique.

- Intégration Hétérogène : La tendance à l’intégration de diverses puces—comme la logique, la mémoire, RF, et analogique—au sein d’un seul paquet empilé s’accélère. Cette approche permet une optimisation des nœuds de processus pour chaque fonction, améliorant la performance globale du système et l’efficacité énergétique. L’association SEMI souligne l’intégration hétérogène comme un catalyseur clé pour des solutions automobiles avancées, 5G et d’informatique en périphérie.

- Innovations en Gestion Thermique : À mesure que l’empilage de dies augmente la densité de puissance, des matériaux thermiques d’interface (TIMs) avancés, le refroidissement microfluidique et des disséminateurs de chaleur intégrés sont développés pour gérer la dissipation thermique. Yole Group rapporte que la gestion thermique efficace est maintenant un facteur de différenciation principal dans la conception des paquets à die empilé, notamment pour les marchés des centres de données et des accélérateurs IA.

- Tests et Inspections Automatisés : La complexité des assemblages à die empilé nécessite des solutions avancées de test et d’inspection, y compris des rayons X haute résolution et la détection de défauts pilotée par IA. KLA Corporation et Teradyne élargissent leurs offres pour relever les défis uniques de fiabilité et de rendement des paquets multi-dies.

Ces tendances technologiques conduisent collectivement le marché de l’emballage de microélectronique à die empilé vers une plus grande intégration, performance et fiabilité, le positionnant comme un catalyseur critique pour les systèmes électroniques de prochaine génération en 2025 et au-delà.

Paysage Concurrentiel et Acteurs Principaux

Le paysage concurrentiel du marché de l’emballage de microélectronique à die empilé en 2025 est caractérisé par une innovation intense, des partenariats stratégiques et un accent sur les capacités de fabrication avancées. Ce secteur est propulsé par la demande de performance accrue des dispositifs, de miniaturisation et d’intégration dans des applications telles que les smartphones, l’informatique haute performance, l’électronique automobile et les dispositifs IoT. Les acteurs clés tirent parti de leur expertise en emballage au niveau des plaquettes, en technologie TSV, et en intégration hétérogène pour maintenir un avantage concurrentiel.

En tête du marché, on trouve des fournisseurs de services d’emballage et d’assemblage de semi-conducteurs bien établis, y compris Amkor Technology, ASE Technology Holding, et TSMC. Ces entreprises ont réalisé des investissements significatifs dans la R&D et la capacité de production pour soutenir la fabrication à haut volume de solutions à die empilé. Par exemple, les technologies avancées CoWoS (Chip-on-Wafer-on-Substrate) et SoIC (System on Integrated Chips) de TSMC sont largement adoptées pour l’informatique haut de gamme et les applications IA, tandis que Amkor Technology et ASE Technology Holding offrent un large portefeuille de services d’emballage 2.5D et 3D pour les marchés de consommation et d’entreprise.

Les IDM (Fabricants de Dispositifs Intégrés) comme Intel Corporation et Samsung Electronics sont également très en vue, intégrant l’emballage à die empilé dans leurs feuilles de route produits pour améliorer la performance des puces et l’efficacité énergétique. La technologie Foveros d’Intel et la plateforme X-Cube de Samsung illustrent des approches propriétaires pour l’intégration verticale et les architectures basées sur des puces modules.

Des acteurs émergents et des spécialistes de niche, tels que JCET Group et Powertech Technology Inc., gagnent du terrain en offrant des solutions personnalisées et en ciblant des verticales spécifiques telles que l’électronique automobile et industrielle. Ces entreprises collaborent souvent avec des sociétés de semi-conducteurs fabless et des intégrateurs de systèmes pour livrer des paquets à die empilé adaptés.

L’environnement concurrentiel est également façonné par des activités de M&A continues, le licensing technologique et des coentreprises, alors que les entreprises cherchent à étendre leurs capacités et leur portée mondiale. Selon Yole Group, le marché devrait continuer à connaître une consolidation, les acteurs majeurs investissant dans des interconnexions de nouvelle génération, des matériaux avancés et l’automatisation pour répondre aux besoins évolutifs des marchés IA, 5G et d’informatique en périphérie.

Prévisions de Croissance du Marché (2025–2030) : TCAC, Analyse des Revenus et des Volumes

Le marché de l’emballage de microélectronique à die empilé est prêt à connaître une forte croissance entre 2025 et 2030, entraînée par une demande croissante de dispositifs électroniques miniaturisés et hautes performances dans les applications d’électronique grand public, d’automobile et de centres de données. Selon les projections de MarketsandMarkets, le marché mondial des circuits intégrés 3D et des solutions d’emballage à die empilé devrait enregistrer un taux de croissance annuel composé (TCAC) d’environ 12 % pendant cette période. Cette trajectoire de croissance est soutenue par l’adoption croissante de solutions d’emballage avancées pour faire face aux limites des architectures 2D traditionnelles, notamment en termes d’efficacité énergétique, de facteur de forme, et de bande passante.

Les prévisions de revenus indiquent que le segment d’emballage de microélectronique à die empilé dépassera les 15 milliards USD d’ici 2030, contre environ 8,5 milliards USD en 2025. Cette explosion est attribuée à la prolifération de l’intelligence artificielle (IA), de l’infrastructure 5G, et de l’informatique en périphérie, qui nécessitent toutes une densité d’interconnexion plus élevée et une gestion thermique améliorée—des avantages clés offerts par les architectures à die empilé. Gartner souligne que le passage de l’industrie des semi-conducteurs vers l’intégration hétérogène et les solutions système-en-emballage (SiP) accélérera encore l’adoption des technologies d’emballage à die empilé.

En termes de volume, le nombre d’unités de dies empilés expédiées devrait croître à un TCAC de 13 à 14 % de 2025 à 2030, reflétant à la fois une pénétration accrue dans les dispositifs de consommation à volume élevé et une utilisation croissante dans l’électronique automobile et l’IoT industriel. Yole Group rapporte que les fonderies et les OSAT (fournisseurs d’assemblage et de test de semi-conducteurs externalisés) leaders augmentent leurs investissements dans des lignes d’emballage avancées pour répondre à cette demande anticipée, l’Asie-Pacifique demeurant le principal pôle de production grâce à son écosystème établi de fabrication de semi-conducteurs.

- TCAC (2025–2030) : 12–14 %

- Revenu (2030) : Plus de 15 milliards USD

- Croissance du Volume : Propulsée par l’électronique grand public, l’automobile et les applications de centres de données

- Régions Clés : L’Asie-Pacifique en tête, suivie par l’Amérique du Nord et l’Europe

Dans l’ensemble, le marché de l’emballage de microélectronique à die empilé est prêt à connaître une expansion significative, propulsée par l’innovation technologique et la poussée incessante vers une plus grande performance et une meilleure intégration dans les systèmes électroniques de prochaine génération.

Analyse du Marché Régional : Amérique du Nord, Europe, Asie-Pacifique et Reste du Monde

Le marché mondial de l’emballage de microélectronique à die empilé connaît une croissance dynamique, avec des tendances régionales façonnées par l’innovation technologique, la demande des utilisateurs finaux et les développements de la chaîne d’approvisionnement. En 2025, les régions Amérique du Nord, Europe, Asie-Pacifique et Reste du Monde (RoW) présentent chacune des caractéristiques de marché distinctes et des moteurs de croissance.

- Amérique du Nord : Le marché nord-américain est propulsé par des investissements robustes dans la fabrication avancée de semi-conducteurs et une forte présence de grandes entreprises technologiques. La région bénéficie d’activités R&D importantes, en particulier aux États-Unis, où la poursuite de la production de puces domestiques est soutenue par des initiatives gouvernementales telles que la loi CHIPS. Les applications clés incluent l’informatique haute performance, l’électronique automobile et les systèmes de défense. Selon Semiconductor Industry Association, l’Amérique du Nord devrait maintenir une croissance stable dans l’emballage à die empilé, stimulée par la demande de solutions miniaturisées et de haute densité dans les infrastructures IA et 5G.

- Europe : Le marché européen se caractérise par un accent sur les applications automobiles, d’automatisation industrielle, et d’IoT. L’accent mis par la région sur la qualité et la fiabilité, ainsi que des normes réglementaires strictes, favorise l’adoption des technologies d’emballage avancées. Des initiatives comme la loi européenne sur les puces visent à renforcer les capacités locales en semi-conducteurs. Selon SEMI, les fabricants européens investissent de plus en plus dans les solutions d’emballage à die empilé pour soutenir les secteurs en pleine croissance des véhicules électriques et de la fabrication intelligente.

- Asie-Pacifique : L’Asie-Pacifique domine le marché mondial de l’emballage de microélectronique à die empilé, représentant la plus grande part en 2025. Ce leadership est soutenu par la présence de grandes fonderies et de fournisseurs OSAT dans des pays tels que Taïwan, la Corée du Sud, la Chine et le Japon. L’adoption rapide de l’électronique grand public, des smartphones et des centres de données alimente la demande d’emballages à haute densité. Selon IC Insights, la croissance du marché de l’Asie-Pacifique est par ailleurs accélérée par des incitations gouvernementales et des expansions de capacité agressives par les acteurs de premier plan.

- Reste du Monde (RoW) : Le segment RoW, incluant l’Amérique Latine, le Moyen-Orient, et l’Afrique, reste naissant mais montre un potentiel de croissance à mesure que les initiatives de transformation numérique s’élargissent. Les investissements dans l’infrastructure de télécommunications et les nouveaux pôles de fabrication électronique devraient progressivement augmenter la demande pour des solutions d’emballage à die empilé, comme l’indique Gartner.

Dans l’ensemble, les dynamiques régionales en 2025 reflètent une convergence d’innovation, de soutien politique et de demande du marché final, l’Asie-Pacifique menant en volume et l’Amérique du Nord et l’Europe se concentrant sur des applications spécialisées à forte valeur ajoutée.

Perspectives Futures : Applications Émergentes et Zones d’Investissement

Les perspectives futures pour l’emballage de microélectronique à die empilé en 2025 sont façonnées par des avancées rapides dans l’intégration des semi-conducteurs, la prolifération de l’IA et de l’informatique haute performance, ainsi que la demande croissante pour des systèmes électroniques miniaturisés et à haute densité. L’emballage à die empilé, qui consiste à intégrer verticalement plusieurs dies de semi-conducteurs dans un seul emballage, est de plus en plus reconnu comme un catalyseur clé pour les dispositifs de prochaine génération dans plusieurs secteurs à forte croissance.

Les applications émergentes sont particulièrement notables dans les centres de données, l’infrastructure 5G et l’informatique en périphérie. Le besoin d’une bande passante plus élevée et d’une latence plus faible dans ces environnements stimule l’adoption d’architectures à die empilé 2.5D et 3D, qui offrent une performance électrique améliorée et des longueurs d’interconnexion réduites. En 2025, l’intégration de la mémoire à haut débit (HBM) avec les dies logiques devrait s’accélérer, soutenant les demandes de calcul des accélérateurs IA et des processeurs graphiques avancés. Des entreprises telles que Samsung Electronics et TSMC investissent massivement dans des lignes d’emballage avancées pour répondre à cette demande.

Une autre application émergente se trouve dans le secteur automobile, où l’emballage à die empilé permet le développement de modules compacts et fiables pour les systèmes avancés d’assistance à la conduite (ADAS) et les véhicules autonomes. Les exigences strictes de l’industrie automobile en matière de gestion thermique et de fiabilité poussent l’innovation dans les technologies d’emballage par vias-silicon (TSV) et au niveau des plaquettes, avec des fournisseurs tels que Infineon Technologies et NXP Semiconductors élargissant leurs portefeuilles pour répondre à ces besoins.

Les zones d’investissement en 2025 devraient se concentrer autour de l’Asie-Pacifique, notamment Taïwan, la Corée du Sud et la Chine, où des incitations gouvernementales et des écosystèmes de fonderie robustes accélèrent la R&D et l’expansion de capacité. Selon Gartner, le marché mondial de l’emballage avancé devrait croître à un TCAC de plus de 7 % jusqu’en 2025, les solutions à die empilé représentant une part significative de cette croissance. Le capital-risque et les investissements stratégiques affluent également vers les startups développant de nouveaux matériaux d’interconnexion et des techniques d’intégration hétérogène, comme le soulignent les récents tours de financements suivis par CB Insights.

- IA et HPC : Emballage à die empilé pour les accélérateurs IA et les GPU

- Automobile : Modules compacts et fiables pour ADAS et véhicules électriques

- 5G/Périphérie : Solutions à faible latence et haut débit pour l’infrastructure réseau

- Asie-Pacifique : Région leader pour l’investissement et l’expansion de fabrication

En résumé, 2025 verra l’emballage de microélectronique à die empilé à la pointe de l’innovation en semi-conducteurs, avec une forte dynamique dans l’IA, l’automobile et les communications, et une activité d’investissement significative en Asie-Pacifique ainsi que dans les startups de matériaux avancés.

Défis, Risques et Opportunités Stratégiques

L’emballage de microélectronique à die empilé, une pierre angulaire de l’intégration avancée des semi-conducteurs, fait face à un paysage complexe de défis et de risques en 2025, mais présente également d’importantes opportunités stratégiques pour les acteurs du secteur. Le principal défi technique reste la gestion thermique. À mesure que davantage de dies sont intégrés verticalement, la dissipation de la chaleur devient de plus en plus problématique, risquant la fiabilité et la dégradation des performances des dispositifs. Des matériaux d’interface thermique avancés et des conceptions innovantes de disséminateurs de chaleur sont en cours d’exploration, mais leur intégration augmente les coûts et la complexité du processus de fabrication (SEMI).

Les risques de rendement et de fiabilité sont également accrus dans les architectures à die empilé. L’augmentation du nombre d’interconnexions, telles que les vias-silicon (TSVs), élève la probabilité de défauts, impactant le rendement global. De plus, l’intégration hétérogène—combinant des dies de différents nœuds de processus ou fonderies—introduit des défis de compatibilité et de test. Le besoin d’outils avancés d’inspection et de métrologie est croissant, mais ces solutions peuvent considérablement augmenter les dépenses en capital (TechInsights).

La complexité de la chaîne d’approvisionnement est un autre risque critique. L’emballage à die empilé nécessite souvent une collaboration avec plusieurs fournisseurs pour les plaquettes, substrats et services d’assemblage. Les perturbations dans n’importe quel segment peuvent retarder la production et augmenter les coûts. Les tensions géopolitiques et les contrôles à l’exportation, en particulier dans le commerce technologique entre les États-Unis et la Chine, aggravent encore les vulnérabilités de la chaîne d’approvisionnement (Gartner).

Malgré ces défis, d’importantes opportunités stratégiques existent. La demande pour l’informatique haute performance, les accélérateurs IA et les dispositifs mobiles avancés pousse une adoption rapide des solutions à die empilé. Les entreprises qui investissent dans la gestion thermique propriétaire, les tests avancés et des stratégies résilientes de chaîne d’approvisionnement peuvent se différencier et capturer des segments de marché premium. De plus, des partenariats entre fonderies, OSAT (assemblage et test de semi-conducteurs externalisés) et fournisseurs EDA (conception électronique automatisée) permettent de nouveaux paradigmes de conception et de fabrication, tels que les architectures basées sur des chiplets, qui peuvent encore débloquer de la valeur (TSMC).

- La gestion thermique et la fiabilité demeurent des obstacles techniques majeurs.

- Les pertes de rendement et les coûts d’inspection augmentent avec la complexité accrue de l’intégration.

- Les risques de chaîne d’approvisionnement sont amplifiés par des facteurs géopolitiques et logistiques.

- Les investissements stratégiques dans la R&D, les partenariats et la résilience de la chaîne d’approvisionnement offrent des avantages concurrentiels.

Sources & Références

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights