2025 Stacked Die Mikroelectromos Csomagolási Piaci Jelentés: Növekedés, Technológiai Változások és Stratégiai Mélyreható Elemzések az Elkövetkező 5 Évre. Fedezze Fel a Kulcsfontosságú Trendeket, Előrejelzéseket és Versenyhelyzetet, Amelyek Formálják az Iparágat.

- Vezetői Összefoglaló és Piaci Áttekintés

- Kulcsfontosságú Technológiai Trendek a Stacked Die Mikroelectromos Csomagolásban

- Versenyhelyzet és Vezető Szereplők

- Piaci Növekedési Előrejelzések (2025–2030): CAGR, Bevételi és Volume Elemzés

- Regionális Piaci Elemzés: Észak-Amerika, Európa, Ázsia-Csendes-óceán és a Világ Még

- Jövőbeli Kilátások: Fejlődő Alkalmazások és Befektetési Központok

- Kihívások, Kockázatok és Stratégiai Lehetőségek

- Források és Hivatkozások

Vezetői Összefoglaló és Piaci Áttekintés

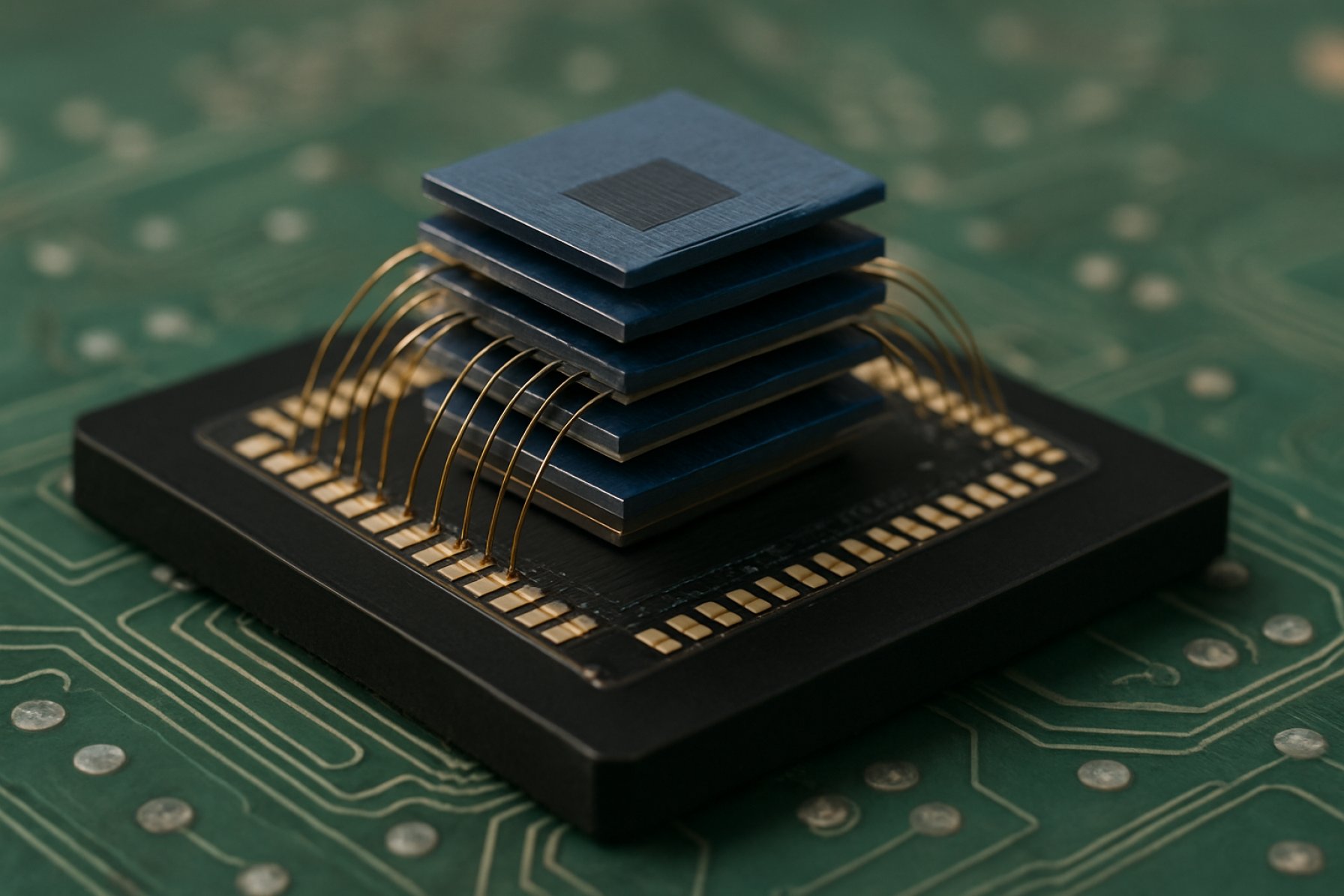

A stacked die mikroelectromos csomagolás több félvezető die integrálását jelenti egyetlen csomagban, függőlegesen elrendezve a tér, a teljesítmény és a funkcionalitás optimalizálása érdekében. Ez a fejlett csomagolási technológia kulcsszerepet játszik a miniaturizálás, a magasabb teljesítmény és az energiahatékonyság folyamatosan növekvő igényeinek kielégítésében olyan szektorokban, mint a fogyasztói elektronika, az autóipar, a távközlés és az adatközpontok. 2025-re a stacked die mikroelectromos csomagolás globális piaca robusztus növekedést mutat, amit az 5G eszközök, a mesterséges intelligencia (AI) alkalmazások és az Internet of Things (IoT) elterjedése hajt.

A Gartner szerint a stacked die csomagolási piac várhatóan 2023 és 2027 között 8%-ot meghaladó éves növekedési ütemet (CAGR) ér el, a bevételek várhatóan 2025-re meghaladják a 12 milliárd dollárt. E növekedés hátterében a 3D integrált áramkörök (3D IC-k), a rendszer-csomagban (SiP) megoldások és a nagy sávszélességű memória (HBM) modulok növekvő elfogadottsága áll, amelyek mind stacked die architektúrákra támaszkodnak a teljesítmény javítása és a méretcsökkentés érdekében.

Kulcsszereplők, mint például a TSMC, a Samsung Electronics és az Intel Corporation jelentős befektetéseket eszközölnek a kutatás és fejlesztés terén, hogy előmozdítsák a fényszűrő vias (TSV) és a wafer-szintű csomagolási (WLP) technológiákat. Ezek az újítások lehetővé teszik a magasabb interkonnekciós sűrűségeket, a jobb hőkezelést és az alacsonyabb energiafogyasztást, amelyek kritikus fontosságúak a következő generációs alkalmazásokban, mint például az AI gyorsítók, a fejlett vezetőtámogató rendszerek (ADAS) és a nagy teljesítményű számítástechnika (HPC).

Regionálisan az Ázsia-Csendes-óceán térség dominálja a stacked die csomagolási piacot, a globális termelési kapacitás több mint 60%-át adja, javarészt a vezető gyártók és az OSAT (kibővített félvezető összeszerelési és tesztelési) szolgáltatók jelenléte miatt olyan országokban, mint Tajvan, Dél-Korea és Kína. Észak-Amerika és Európa is növekvő elfogadást mutat, különösen az autóipari elektronika és az adatközponti infrastruktúra területén, ahogyan azt az IC Insights is megjegyzi.

Összefoglalva, a stacked die mikroelectromos csomagolás a félvezető ipar 2025-ös fejlődésének alapvető technológiája, amely lehetővé teszi a magasabb integrációt, teljesítményt és hatékonyságot egy széles spektrumú alkalmazásban. A piac fejlődési irányát a folyamatban lévő technológiai újítások, a vezető szereplők stratégiai befektetései és a folyamatosan növekvő kereslet formálja a intelligens, kisebb és erősebb elektronikai rendszerek iránt.

Kulcsfontosságú Technológiai Trendek a Stacked Die Mikroelectromos Csomagolásban

A stacked die mikroelectromos csomagolás a félvezető újítás élvonalában áll, lehetővé téve a magasabb eszköz teljesítményt, fokozott funkcionalitást és csökkentett méretet azáltal, hogy több félvezető die-t integrál egyetlen csomagban függőlegesen. Ahogy az ipar 2025 felé halad, számos kulcsfontosságú technológiai trend formálja a stacked die csomagolási megoldások fejlődését és elfogadását.

- Fejlett Fényszűrő Vias (TSV) Integráció: A TSV technológia továbbra is alapvető fontosságú a nagy sűrűségű die halmozás szempontjából, alacsony késleltetésű, nagy sávszélességű interkonnekciókat kínálva a függőlegesen elrendezett die-ok között. 2025-re a gyártók finomítják a TSV folyamatokat a via átmérőjének és távolságának csökkentésével, így növelve az interkonnex sűrűséget és javítva az elektromos teljesítményt. Ez különösen kritikus a nagy teljesítményű számítástechnika (HPC) és a mesterséges intelligencia (AI) alkalmazások számára, ahol a memória sávszélessége szűk keresztmetszet. A TSMC és a Samsung Electronics vezetőséget vállal a fejlett TSV-alapú 2.5D és 3D IC csomagolás kereskedelembe hozatalában.

- Hibrid Összekapcsolási Technikák: A hibrid összekapcsolás, amely a közvetlen réz-re réz és dielektromos dielektromos összekapcsolást kombinálja, egyre népszerűbb módszer az ultra-finom távolságú összekapcsolások és a javított elektromos jellemzők elérésére. Ez a technológia lehetővé teszi a 10 mikron alatti távolságú halmozást, amely elengedhetetlen a következő generációs logikai-memória integrációhoz. Az Amkor Technology és az Intel Corporation jelentős beruházásokat jelentett be a hibrid összekapcsolásba mind a memória, mind a logikai eszközök esetében.

- Heterogén Integráció: Az a tendencia, hogy különböző chipleteket – például logikát, memóriát, RF-et és analóg technológiákat – integrálnak egyetlen stacked csomagba, gyorsan terjed. Ez a megközelítés lehetővé teszi a funkcionalitáshoz legjobban illeszkedő feldolgozási csomópontok optimalizálását, javítva az általános rendszer teljesítményét és energiahatékonyságát. A SEMI iparági szövetség hangsúlyozza a heterogén integrációt, mint a fejlett autóipari, 5G és edge computing megoldások kulcsfontosságú támogatója.

- Hőkezelési Újítások: Mivel a die halmozás növeli a teljesítmény sűrűségét, fejlett hőinterface anyagok (TIM), mikrofluidikus hűtés és integrált hőelvezetők fejlesztése zajlik a hőelvezetés kezelésére. A Yole Group jelentése szerint a hatékony hőkezelés ma már kulcsfontosságú különbségképző a stacked die csomagolás tervezésében, különösen az adatközponti és AI gyorsító piacokon.

- Automatizált Tesztelés és Ellenőrzés: A stacked die összeszerelés összetettsége fejlett tesztelési és ellenőrzési megoldásokat igényel, beleértve a nagy felbontású röntgent és az AI-vezérelt hibafelismerést. A KLA Corporation és a Teradyne bővítik kínálatukat, hogy megoldják a több die csomag megbízhatósági és hozamdifficulties-specifikus kihívásokat.

Ezek a technológiai trendek összességében előremozdítják a stacked die mikroelectromos csomagolás piacát a nagyobb integráció, teljesítmény és megbízhatóság felé, amivel jelentős támogatója a következő generációs elektronikai rendszereknek 2025-ben és azon túl.

Versenyhelyzet és Vezető Szereplők

A stacked die mikroelectromos csomagolási piac versenyhelyzete 2025-re intenzív innovációt, stratégiai partnerségeket és a fejlett gyártási képességekre összpontosít. E szektorot a magasabb eszköz teljesítmény, a miniaturizáció és az integráció iránti kereslet hajtja olyan alkalmazásokban, mint az okostelefonok, a nagy teljesítményű számítástechnika, az autóipari elektronika és az IoT eszközök. A kulcsszereplők szakértelmüket használják fel a wafer-szintű csomagolásban, a fényszűrő vias (TSV) technológiában és a heterogén integrációban, hogy versenyelőnyre tegyenek szert.

Jeles piaci szereplők közé tartoznak a megalapozott félvezető csomagoló és összeszerelő szolgáltatók, mint Amkor Technology, ASE Technology Holding és TSMC. Ezek a cégek jelentős beruházásokat eszközöltek a K&F és a gyártó kapacitás terén, hogy támogassák a stacked die megoldások nagy volumenű gyártását. Például a TSMC fejlett CoWoS (Chip-on-Wafer-on-Substrate) és SoIC (System on Integrated Chips) technológiái széles körben elfogadottak a csúcsminőségű számítástechnikai és AI alkalmazásokhoz, míg Az Amkor Technology és ASE Technology Holding egy széles portfóliót kínál a 2.5D és 3D csomagolási szolgáltatásokból a fogyasztói és vállalati piacokon.

IDM-ek (Integrált Gyártó Vállalatok), mint az Intel Corporation és a Samsung Electronics szintén prominens szereplők, amelyek integrálják a stacked die csomagolást terméktervükbe a chip teljesítményének és energiahatékonyságának javítása érdekében. Az Intel Foveros technológiája és a Samsung X-Cube platformja példák az egyedi megoldásokra a vertikális integráció és chiplet-alapú architektúrák terén.

Fejlődő szereplők és niche specialisták, például JCET Group és Powertech Technology Inc., növekvő figyelmet kapnak, testreszabott megoldásokat kínálva és célzott függvényekre összpontosítva, például az autóipar és az ipari elektronika területén. Ezek a cégek gyakran együttműködnek fabless félvezető cégekkel és rendszerintegrátorokkal, hogy testreszabott stacked die csomagokat nyújtsanak.

A versenykörnyezetet tovább alakítja a folyamatos M&A tevékenység, a technológiai licencelés és a közös vállalkozások, mivel a cégek bővíteni kívánják képességeiket és globális elérhetőségüket. A Yole Group szerint a piac várhatóan további konszolidáción fog keresztülmenni, a vezető szereplők a következő generációs interkonnexek, fejlett anyagok és automatizálás iránti befektetéseket eszközölnek, hogy reagáljanak az AI, 5G és edge computing piacok változó igényeire.

Piaci Növekedési Előrejelzések (2025–2030): CAGR, Bevételi és Volume Elemzés

A stacked die mikroelectromos csomagolási piac 2025 és 2030 között jelentős növekedés előtt áll, amit a nagy teljesítményű, miniaturizált elektronikai eszközök iránti növekvő kereslet generál a fogyasztói elektronika, az autóipar és az adatközponti alkalmazások terén. Az MarketsandMarkets előrejelzései szerint a globális 3D IC és stacked die csomagolási piac várhatóan 12%-os éves növekedési ütemet (CAGR) jegyez fel ebben az időszakban. E növekedés alapját az fejlett csomagolási megoldások növekvő elfogadása képezi, amelyek célja a hagyományos 2D architektúrák korlátainak leküzdése, különösen az energiahatékonyság, a formafaktor és a sávszélesség terén.

A bevételi előrejelzések szerint a stacked die mikroelectromos csomagolás szegmens 2030-ra meghaladja a 15 milliárd USD-t, szemben az 2025-re becsült 8,5 milliárd USD-val. E növekedés mögött a mesterséges intelligencia (AI), az 5G infrastruktúra és az edge computing elterjedése áll, amelyek mind magukban foglalják a magasabb interkonnex sűrűséget és a jobb hőkezelést – a stacked die architektúrák által nyújtott kulcsfontosságú előnyöket. A Gartner kiemeli, hogy a félvezető ipar heterogén integráció és rendszer-csomag (SiP) megoldások felé történő elmozdulása tovább gyorsítja a stacked die csomagolási technológiák elfogadását.

Volume szempontjából a szállított stacked die egységek száma várhatóan 13-14%-os CAGR-t növekedést mutat 2025 és 2030 között, tükrözve a nagy volumenű fogyasztói eszközök jobb penetrációját és az autóipari elektronika és ipari IoT bővülő használatát. A Yole Group szerint a vezető gyártók és az OSAT-ok (Kibővített Félvezető Összeszerelő és Tesztelési szolgáltatók) fokozaotttan fejlesztik a fejlett csomagolási vonalaikat, hogy megfeleljenek e várható keresletnek, az Ázsia-Csendes-óceán térség pedig továbbra is a domináns termelési központ, mivel meglévő félvezető gyártási ökoszisztémával rendelkezik.

- CAGR (2025–2030): 12–14%

- Bevétel (2030): 15+ milliárd USD

- Volume Növekedés: Fogyasztói elektronika, autóipar és adatközponti alkalmazások hajtják

- Kulcsfontosságú Régiók: Ázsia-Csendes-óceán vezet, azt követi Észak-Amerika és Európa

Összességében a stacked die mikroelectromos csomagolás piaca jelentős bővülés előtt áll, amelyet a technológiai innováció és a következő generációs elektronikai rendszerekben a magasabb teljesítmény és integráció iránti folyamatos igény hajt.

Regionális Piaci Elemzés: Észak-Amerika, Európa, Ázsia-Csendes-óceán és a Világ Még

A stacked die mikroelectromos csomagolás globális piaca dinamikus növekedést mutat, a regionális trendeket a technológiai innováció, a felhasználói kereslet és a beszállítói lánc fejlődése alakítja. 2025-re Észak-Amerika, Európa, Ázsia-Csendes-óceán és a Világ Még (RoW) régiók mindegyike a saját piaci jellemzőkkel és növekedési hajtóerőkkel rendelkezik.

- Észak-Amerika: Az észak-amerikai piacot jelentős invesztíciók hajtják az innovatív félvezető gyártás terén és a vezető technológiai cégek erős jelenléte. A térség nagy mértékben használja a K&F tevékenységet, különösen az Egyesült Államokban, ahol a hazai chipgyártás iránti nyomást a kormányzati kezdeményezések, mint például a CHIPS törvény, támogatják. A kulcsfontosságú alkalmazások a nagy teljesítményű számítástechnika, az autóipari elektronika és a védelmi rendszerek. Az Félvezető Iparág Szövetsége szerint Észak-Amerika várhatóan folyamatos növekedést mutat a stacked die csomagolásban, amit a miniaturizált, nagy sűrűségű megoldások iránti kereslet hajt az AI és 5G infrastruktúrában.

- Európa: Európa piacát autóipari, ipari automatizálás és IoT alkalmazások iránti fókusz jellemzi. A térség minőségre és megbízhatóságra helyezett hangsúlya, junto a szigorú szabályozási normák, támogatja a fejlett csomagolási technológiák elfogadását. Az európai Chip törvény célja a helyi félvezető képességek erősítése. A SEMI szerint az európai gyártók egyre nagyobb mértékben fektetnek be a stacked die megoldásokba, hogy támogassák a térség növekvő elektromos jármű és okosgyártási szektorait.

- Ázsia-Csendes-óceán: Az Ázsia-Csendes-óceán a stacked die mikroelectromos csomagolás globális piacának domináló részesedésével bír, amely 2025-re a legnagyobb részesedést képviseli. E vezető szerep mögött a jelentős gyártók és az OSAT (Kibővített Félvezető Összeszerelési és Tesztelési) szolgáltatók jelenléte áll olyan országokban, mint Tajvan, Dél-Korea, Kína és Japán. A térség gyors elfogadása a fogyasztói elektronika, smartphones és adatközpontok gyorsan növeli a keresletet a nagy sűrűségű csomagolás iránt. Az IC Insights szerint az Ázsia-Csendes-óceán piaci növekedését a kormányzati ösztönzők és a vezető szereplők agresszív kapacitásbővítése gyorsítja.

- Világ Még (RoW): A RoW szegmens, beleértve Latin-Amerikát, a Közel-Keletet és Afrikát, még gyerekcipőben jár, de növekedési potenciállal bír ahogy a digitális átalakulási kezdeményezések bővülnek. A távközlési infrastruktúrába tett befektetések és a feltörekvő elektronikai gyártási központok várhatóan fokozatosan növelik a stacked die csomagolási megoldások iránti keresletet, ahogyan azt a Gartner is megjegyzi.

Összességében a regionális dinamikák 2025-re az innováció, a politikai támogatás és a végpiaci kereslet egybeesését tükrözik, Ázsia-Csendes-óceán térsége vezet a volument illetően, míg Észak-Amerika és Európa a magas értékű, specializált alkalmazásokra összpontosít.

Jövőbeli Kilátások: Fejlődő Alkalmazások és Befektetési Központok

A stacked die mikroelectromos csomagolás jövőbeli kilátásait 2025-re a félvezető integráció gyors fejlődése, az AI és a nagy teljesítményű számítástechnika elterjedése, valamint a miniaturizált, nagysűrűségű elektronikai rendszerek növekvő kereslete alakítja. A stacked die csomagolás, amely magában foglalja több félvezető die függőleges integrációját egyetlen csomagban, egyre inkább kulcsszereplővé válik a következő generációs eszközök fejlesztésében több nagy növekedésű szektorban.

Az új alkalmazások különösen hangsúlyosak az adatközpontokban, az 5G infrastruktúrában és az edge computing területén. Az e környezetekben a nagyobb sávszélesség és a kisebb késleltetés iránti igény gyorsítja a 2.5D és 3D stacked die architektúrák elterjedését, amelyek javított elektromos teljesítményt és csökkentett interkonnex hosszt kínálnak. 2025-re a nagy sebességű memória (HBM) és a logikai die-k integrálása várhatóan felgyorsul, támogatva az AI gyorsítók és fejlett grafikus processzorok számítási igényeit. Olyan cégek, mint a Samsung Electronics és a TSMC, jelentős beruházásokat eszközölnek a fejlett csomagolási vonalak kialakítására, hogy megfeleljenek e keresletnek.

Egy másik fejlődő alkalmazás az autóiparban tapasztalható, ahol a stacked die csomagolás lehetővé teszi a kompakt, nagy megbízhatóságú modulok kifejlesztését a fejlett vezetőtámogató rendszerek (ADAS) és az autonóm járművek számára. Az autóipar szigorú követelményei a hőkezelés és a megbízhatóság terén innovációt ösztönöznek a fényszűrő vias (TSV) és a wafer-szintű csomagolási technológiák terén, a szállítók, mint például Infineon Technologies és NXP Semiconductors bővíti portfólióját, hogy kielégítse ezeket az igényeket.

A 2025-ös befektetési központok várhatóan az Ázsia-Csendes-óceán térségre összpontosítanak, különösen Tajvanra, Dél-Koreára és Kínára, ahol a kormányzati ösztönzők és a robusztus gyártási ökoszisztémák felgyorsítják a K&F és kapacitásbővítést. A Gartner szerint a globális fejlett csomagolási piac várhatóan 7%-os CAGR-t növekedést mutat 2025-ig, a stacked die megoldások pedig e növekedés jelentős részét adják. A kockázati tőke és stratégiai befektetések is áramlanak a startupok felé, amelyek új interkonnex anyagok és heterogén integrációs technikák fejlesztésével foglalkoznak, ahogyan azt az az CB Insights által nyomon követett legutóbbi finanszírozási körök hangsúlyozzák.

- AI és HPC: Stacked die csomagolás AI gyorsítók és GPU-k számára

- Autóipar: Nagy megbízhatóságú, kompakt modulok ADAS és EV-k számára

- 5G/Edge: Alacsony késleltetésű, nagy sávszélességű megoldások hálózati infrastruktúrához

- Ázsia-Csendes-óceán: Vezető régió a befektetés és a gyártási expanzió terén

Összefoglalva, 2025-ben a stacked die mikroelectromos csomagolás a félvezető innováció előterében áll, erős lendülettel az AI, az autóipar és a kommunikáció terén, és jelentős befektetési aktivitás várható az Ázsia-Csendes-óceán térségében és a fejlett anyagok startupjaiban.

Kihívások, Kockázatok és Stratégiai Lehetőségek

A stacked die mikroelectromos csomagolás, mint az fejlett félvezető integráció sarokköve, egy összetett kihívásokkal és kockázatokkal teli táj előtt áll 2025-ben, de egyben jelentős stratégiai lehetőségeket is kínál az iparág szereplőinek. A legnagyobb technikai kihívás továbbra is a hőkezelés. Ahogy egyre több die integrálódik függőlegesen, a hőelvezetés egyre problémásabbá válik, ami kockáztatja az eszközök megbízhatóságát és a teljesítmény csökkenését. Fejlett hőinterface anyagok és innovatív hőelvezető tervek kutatása zajlik, de ezek integrálása költséget és bonyolultságot ad a gyártási folyamathoz (SEMI).

A hozam és a megbízhatósági kockázatok is növekvő mértékben megjelennek a stacked die architektúrákban. A megnövekedett számú interkonnex, mint a fényszűrő viasok (TSV), növeli a hibák valószínűségét, ami hatással van az általános hozamra. Ezen túlmenően a heterogén integráció – különböző feldolgozási csomópontokból vagy gyártóktól származó die-ok kombinálása – kompatibilitási és tesztelési kihívásokat okoz. A fejlett ellenőrzési és metrológiai eszközök iránti kereslet nő, de ezek a megoldások jelentősen megnövelhetik a tőkebefektetést (TechInsights).

A beszállítói lánc bonyolultsága szintén egy kritikus kockázat. A stacked die csomagolás gyakran követeli meg, hogy a gyártás különböző szállítókkal működjön együtt a wafer-ek, szubsztrátumok és összeszerelési szolgáltatások terén. Az egyes szegmensekben bekövetkező zavarok késlekedéseket okozhatnak a gyártásban és növelhetik a költségeket. A geopolitikai feszültségek és az exportellenőrzések, különösen az Egyesült Államok és Kína technológiai kereskedelme terén, tovább súlyosbítják a beszállítói lánc sebezhetőségét (Gartner).

A kihívások ellenére számos stratégiai lehetőség rejlik. A nagy teljesítményű számítástechnika, AI gyorsítók és fejlett mobil eszközök iránti kereslet gyorsítja a stacked die megoldások elterjedését. Azok a cégek, amelyek beruháznak a szabadalmi hőkezelési, fejlett tesztelési és robusztus beszállítói lánc stratégiákba, megkülönböztethetik magukat és megszerezhetik a prémium piaci szegmenseket. Ezen túlmenően a gyártók, OSAT-ok (kibővített félvezető összeszerelési és tesztelési), és EDA (Elektronikus Tervezési Automatizáció) szolgáltatók közötti partnerségek új tervezési és gyártási paradigmákat tesznek lehetővé, mint például chiplet-alapú architektúrák, amelyek további értékeket szabadíthatnak fel (TSMC).

- A hőkezelés és a megbízhatóság a legfontosabb technikai kihívások.

- A hozamcsökkenés és a tesztelési költségek növekednek a fokozott integrációs komplexitással.

- A beszállítói lánc kockázatai fokozódnak geopolitikai és logisztikai tényezők miatt.

- A K&F, partnerségek és a beszállítói lánc ellenálló képességére irányuló stratégiai befektetések versenyelőnyöket kínálnak.

Források és Hivatkozások

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Félvezető Iparág Szövetsége

- Infineon Technologies

- NXP Semiconductors

- TechInsights