Rapporto sul Mercato del Packaging Microelettronico con Dies Impilati 2025: Crescita, Cambiamenti Tecnologici e Approfondimenti Strategici per i Prossimi 5 Anni. Esplora Tendenze Chiave, Previsioni e Dinamiche Competitive che Modellano l’Industria.

- Riepilogo Esecutivo & Panoramica del Mercato

- Principali Tendenze Tecnologiche nel Packaging Microelettronico con Dies Impilati

- Panorama Competitivo e Attori Principali

- Previsioni di Crescita del Mercato (2025–2030): CAGR, Analisi dei Ricavi e dei Volumi

- Analisi del Mercato Regionale: Nord America, Europa, Asia-Pacifico e Resto del Mondo

- Prospettive Future: Applicazioni Emergenti e Punti Caldi di Investimento

- Sfide, Rischi e Opportunità Strategiche

- Fonti & Riferimenti

Riepilogo Esecutivo & Panoramica del Mercato

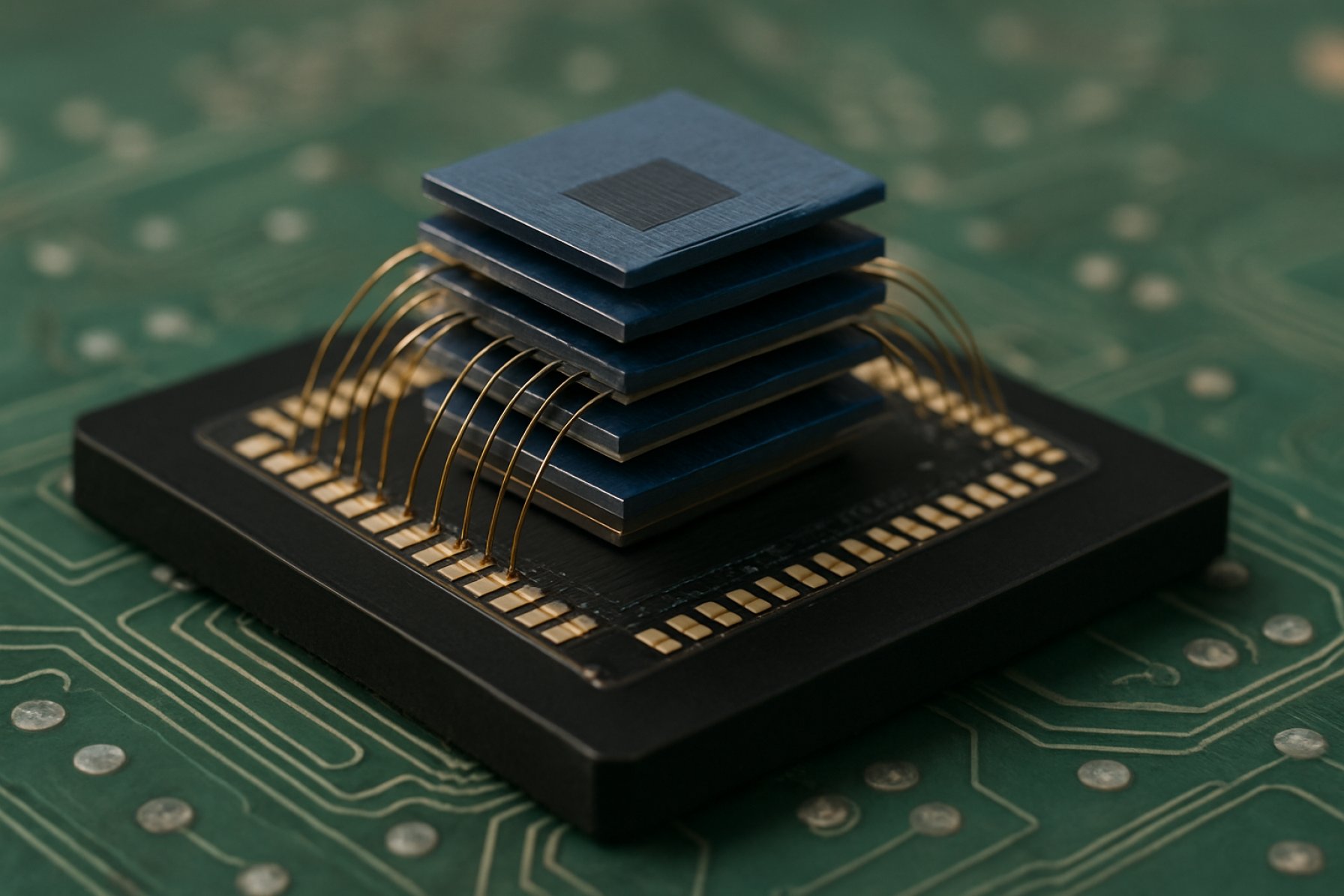

Il packaging microelettronico con dies impilati si riferisce all’integrazione di più chip semiconduttori all’interno di un unico pacchetto, disposti verticalmente per ottimizzare spazio, performance e funzionalità. Questa tecnologia avanzata di packaging è fondamentale per soddisfare le crescenti richieste di miniaturizzazione, alte prestazioni e efficienza energetica in settori come l’elettronica di consumo, l’automotive, le telecomunicazioni e i data center. A partire dal 2025, il mercato globale del packaging microelettronico con dies impilati sta vivendo una forte crescita, alimentata dalla proliferazione di dispositivi 5G, applicazioni di intelligenza artificiale (AI) e Internet delle Cose (IoT).

Secondo Gartner, il mercato del packaging con dies impilati è previsto registrare un tasso di crescita annuale composto (CAGR) superiore all’8% tra il 2023 e il 2027, con ricavi che si prevede supereranno i 12 miliardi di dollari entro il 2025. Questa crescita è sostenuta dall’aumento dell’adozione di circuiti integrati 3D (3D ICs), soluzioni di sistema-in-pacchetto (SiP) e moduli di memoria ad alta larghezza di banda (HBM), tutti progettati per sfruttare architetture a dies impilati per offrire prestazioni migliorate e formati ridotti.

Attori chiave del settore, come TSMC, Samsung Electronics e Intel Corporation, stanno investendo pesantemente in ricerca e sviluppo per avanzare nelle tecnologie di via attraverso il silicio (TSV) e di packaging a livello di wafer (WLP). Queste innovazioni stanno consentendo densità di interconnessione più elevate, gestione termica migliorata e riduzione del consumo energetico, elementi critici per applicazioni di nuova generazione in acceleratori AI, sistemi avanzati di assistenza al conducente (ADAS) e calcolo ad alte prestazioni (HPC).

A livello regionale, l’Asia-Pacifico domina il mercato del packaging con dies impilati, rappresentando oltre il 60% della capacità produttiva globale, principalmente grazie alla presenza di fonderie leader e fornitori di OSAT (assemblaggio e test di semiconduttori esternalizzati) in paesi come Taiwan, Corea del Sud e Cina. Anche il Nord America e l’Europa stanno assistendo a un crescente interesse, in particolare nell’elettronica automobilistica e nelle infrastrutture dei data center, come notato da IC Insights.

In sintesi, il packaging microelettronico con dies impilati rappresenta una tecnologia fondamentale per l’evoluzione dell’industria dei semiconduttori nel 2025, consentendo una maggiore integrazione, prestazioni ed efficienza in un ampio spettro di applicazioni. La traiettoria del mercato è influenzata da continui progressi tecnologici, investimenti strategici da parte degli attori principali e dalla richiesta incessante di sistemi elettronici più intelligenti, più piccoli e più potenti.

Principali Tendenze Tecnologiche nel Packaging Microelettronico con Dies Impilati

Il packaging microelettronico con dies impilati è all’avanguardia dell’innovazione nei semiconduttori, consentendo prestazioni superiori dei dispositivi, maggiore funzionalità e formati ridotti grazie all’integrazione verticale di più chip semiconduttori all’interno di un unico pacchetto. Con il progredire dell’industria verso il 2025, diverse tendenze tecnologiche chiave stanno plasmando l’evoluzione e l’adozione delle soluzioni di packaging con dies impilati.

- Integrazione Avanzata delle VIE Attraverso il Silicio (TSV): La tecnologia TSV rimane un punto di riferimento per l’impilamento ad alta densità dei chip, offrendo interconnessioni a bassa latenza e alta larghezza di banda tra i chip allineati verticalmente. Nel 2025, i produttori stanno perfezionando i processi TSV per ridurre il diametro e l’interasse delle vie, aumentando così la densità di interconnessione e migliorando le prestazioni elettriche. Questo è particolarmente critico per applicazioni di calcolo ad alte prestazioni (HPC) e intelligenza artificiale (AI), dove la larghezza di banda della memoria rappresenta un collo di bottiglia. TSMC e Samsung Electronics sono in prima linea nella commercializzazione di packaging IC 2.5D e 3D basato su TSV.

- Tecniche di Bonding Ibrido: Il bonding ibrido, che combina il bonding diretto rame-su-rame e dielettrico-su-dielettrico, sta guadagnando terreno come metodo per ottenere interconnessioni a passo ultra-fine e caratteristiche elettriche migliorate. Questa tecnologia sta consentendo impilamenti a passo inferiore ai 10 micron, essenziali per l’integrazione logica-memoria di nuova generazione. Amkor Technology e Intel Corporation hanno annunciato significativi investimenti nel bonding ibrido sia per dispositivi di memoria che per dispositivi logici.

- Integrazione Eterogenea: La tendenza verso l’integrazione di chiplet diversi—come logica, memoria, RF e analogici—all’interno di un unico pacchetto impilato è in accelerazione. Questo approccio consente di ottimizzare i nodi di processo per ciascuna funzione, migliorando le prestazioni e l’efficienza energetica del sistema. L’associazione industriale SEMI evidenzia l’integrazione eterogenea come un facilitatore chiave per soluzioni avanzate nel settore automotive, 5G e calcolo edge.

- Innovazioni nella Gestione Termica: Con l’aumento della densità di potenza causata dall’impilamento dei chip, vengono sviluppati materiali interfaciali termici (TIM) avanzati, raffreddamento microfluidico e dissipatori di calore integrati per gestire la dissipazione del calore. Yole Group riporta che una gestione termica efficace è ora un differenziatore primario nel design dei pacchetti a dies impilati, soprattutto per i mercati dei data center e degli acceleratori AI.

- Test e Ispezione Automatici: La complessità degli assemblaggi a dies impilati richiede soluzioni avanzate di test e ispezione, tra cui raggi X ad alta risoluzione e rilevazione difetti guidata da intelligenza artificiale. KLA Corporation e Teradyne stanno espandendo la loro offerta per affrontare le sfide uniche della affidabilità e del rendimento dei pacchetti multi-die.

Queste tendenze tecnologiche stanno collettivamente guidando il mercato del packaging microelettronico con dies impilati verso una maggiore integrazione, prestazioni e affidabilità, posizionandolo come un facilitatore critico per i sistemi elettronici di nuova generazione nel 2025 e oltre.

Panorama Competitivo e Attori Principali

Il panorama competitivo del mercato del packaging microelettronico con dies impilati nel 2025 è caratterizzato da intensa innovazione, partnership strategiche e un focus su capacità produttive avanzate. Questo settore è guidato dalla domanda di prestazioni elevate dei dispositivi, miniaturizzazione e integrazione in applicazioni come smartphone, calcolo ad alte prestazioni, elettronica automobilistica e dispositivi IoT. I principali attori stanno sfruttando la loro esperienza nel packaging a livello di wafer, nella tecnologia TSV e nell’integrazione eterogenea per mantenere un vantaggio competitivo.

Nella parte alta del mercato si trovano fornitori consolidati di packaging e servizi di assemblaggio di semiconduttori, tra cui Amkor Technology, ASE Technology Holding e TSMC. Queste aziende hanno effettuato significativi investimenti in R&D e capacità produttiva per supportare la produzione ad alto volume di soluzioni con dies impilati. Ad esempio, le tecnologie avanzate CoWoS (Chip-on-Wafer-on-Substrate) e SoIC (System on Integrated Chips) di TSMC sono ampiamente adottate per applicazioni di calcolo e AI di fascia alta, mentre Amkor Technology e ASE Technology Holding offrono un ampio portafoglio di servizi di packaging 2.5D e 3D per mercati consumer e enterprise.

IDM (Integrated Device Manufacturers) come Intel Corporation e Samsung Electronics sono anch’essi prominenti, integrando il packaging con dies impilati nelle loro roadmap di prodotto per migliorare le prestazioni e l’efficienza energetica dei chip. La tecnologia Foveros di Intel e la piattaforma X-Cube di Samsung esemplificano approcci proprietari all’integrazione verticale e alle architetture basate su chiplet.

Attori emergenti e specialisti di nicchia, tra cui JCET Group e Powertech Technology Inc., stanno guadagnando terreno offrendo soluzioni personalizzate e mirando a verticali specifici come l’elettronica automobilistica e industriale. Queste aziende collaborano spesso con società di semiconduttori senza fab e integratori di sistemi per fornire pacchetti a dies impilati su misura.

L’ambiente competitivo è ulteriormente plasmato da un’attività continua di fusioni e acquisizioni, licenze tecnologiche e joint venture, poiché le aziende cercano di espandere le proprie capacità e la propria portata globale. Secondo Yole Group, si prevede che il mercato continuerà a vedere consolidamenti, con attori leader che investono in interconnessioni di nuova generazione, materiali avanzati e automazione per affrontare le esigenze in evoluzione dei mercati AI, 5G e calcolo edge.

Previsioni di Crescita del Mercato (2025–2030): CAGR, Analisi dei Ricavi e dei Volumi

Il mercato del packaging microelettronico con dies impilati è pronto a una robusta crescita tra il 2025 e il 2030, guidata dalla crescente domanda di dispositivi elettronici miniaturizzati e ad alte prestazioni in applicazioni di elettronica di consumo, automotive e data center. Secondo le proiezioni di MarketsandMarkets, il mercato globale dei circuiti integrati 3D e del packaging con dies impilati dovrebbe registrare un tasso di crescita annuale composto (CAGR) di circa il 12% durante questo periodo. Questa traiettoria di crescita è sostenuta dall’aumento dell’adozione di soluzioni di packaging avanzato per affrontare le limitazioni delle architetture 2D tradizionali, in particolare in termini di efficienza energetica, fattore di forma e larghezza di banda.

Le previsioni sui ricavi indicano che il segmento del packaging microelettronico con dies impilati supererà i 15 miliardi di dollari USA entro il 2030, rispetto a una stima di 8,5 miliardi di dollari nel 2025. Questo aumento è attribuito alla proliferazione dell’intelligenza artificiale (AI), delle infrastrutture 5G e del calcolo edge, tutti elementi che richiedono una maggiore densità di interconnessione e una gestione termica migliorata—vantaggi chiave offerti dalle architetture a dies impilati. Gartner sottolinea che il passaggio dell’industria dei semiconduttori verso l’integrazione eterogenea e le soluzioni di sistema-in-pacchetto (SiP) accelererà ulteriormente l’adozione delle tecnologie di packaging con dies impilati.

In termini di volume, il numero di unità a dies impilati spedite dovrebbe crescere con un CAGR del 13–14% dal 2025 al 2030, riflettendo sia una maggiore penetrazione nei dispositivi consumer ad alto volume che un uso in espansione nell’elettronica automobilistica e nell’IoT industriale. Yole Group riporta che le fonderie leader e le OSAT (Fornitori di Assemblaggio e Test di Semiconduttori Esternalizzati) stanno intensificando gli investimenti in linee di packaging avanzato per soddisfare questa domanda attesa, con l’Asia-Pacifico che rimane il principale polo di produzione grazie al suo ecosistema di produzione di semiconduttori consolidato.

- CAGR (2025–2030): 12–14%

- Ricavi (2030): Oltre 15 miliardi di dollari USA

- Crescita del Volume: Guidata da applicazioni di elettronica di consumo, automotive e data center

- Regioni Chiave: L’Asia-Pacifico guida, seguita da Nord America e Europa

In generale, il mercato del packaging microelettronico con dies impilati è destinato a un’espansione significativa, sostenuta dall’innovazione tecnologica e dalla spinta incessante verso prestazioni e integrazione superiori nei sistemi elettronici di nuova generazione.

Analisi del Mercato Regionale: Nord America, Europa, Asia-Pacifico e Resto del Mondo

Il mercato globale del packaging microelettronico con dies impilati sta vivendo una crescita dinamica, con tendenze regionali plasmate dall’innovazione tecnologica, dalla domanda degli utenti finali e dai sviluppi della catena di approvvigionamento. Nel 2025, i mercati del Nord America, Europa, Asia-Pacifico e Resto del Mondo (RoW) presentano ciascuno caratteristiche di mercato distinte e motori di crescita.

- Nord America: Il mercato nordamericano è spinto da investimenti robusti nella produzione avanzata di semiconduttori e dalla forte presenza di aziende tecnologiche leader. La regione beneficia di significative attività di R&D, in particolare negli Stati Uniti, dove l’iniziativa per la produzione domestica di chip è supportata da iniziative governative come il CHIPS Act. Le applicazioni chiave includono calcolo ad alte prestazioni, elettronica automobilistica e sistemi di difesa. Secondo Semiconductor Industry Association, si prevede che il Nord America manterrà una crescita costante nel packaging a dies impilati, guidata dalla domanda di soluzioni miniaturizzate e ad alta densità nelle infrastrutture AI e 5G.

- Europa: Il mercato europeo è caratterizzato da un focus su applicazioni automobilistiche, automazione industriale e IoT. L’enfasi della regione sulla qualità e l’affidabilità, insieme a standard regolatori rigorosi, favorisce l’adozione di tecnologie di packaging avanzato. Iniziative come il Chips Act europeo mirano a potenziare le capacità locali dei semiconduttori. Secondo SEMI, i produttori europei stanno incrementando gli investimenti in soluzioni con dies impilati per supportare i settori dell’elettrico e della produzione intelligente in crescita della regione.

- Asia-Pacifico: L’Asia-Pacifico domina il mercato globale del packaging microelettronico con dies impilati, rappresentando la quota maggiore nel 2025. Questa leadership è sostenuta dalla presenza di importanti fonderie e fornitori di OSAT (Assemblaggio e Test di Semiconduttori Esternalizzati) in paesi come Taiwan, Corea del Sud, Cina e Giappone. La rapida adozione di elettronica di consumo, smartphone e data center nella regione alimenta la domanda di packaging ad alta densità. Secondo IC Insights, la crescita del mercato dell’Asia-Pacifico è ulteriormente accelerata da incentivi governativi e pressoché significativi ampliamenti di capacità da parte degli attori leader.

- Resto del Mondo (RoW): Il segmento RoW, che comprende America Latina, Medio Oriente e Africa, rimane ancora agli inizi ma mostra potenziale di crescita man mano che le iniziative di trasformazione digitale si espandono. Gli investimenti nelle infrastrutture di telecomunicazioni e nei nuovi hub di produzione elettronica si prevede aumenteranno gradualmente la domanda di soluzioni di packaging con dies impilati, come notato da Gartner.

In generale, le dinamiche regionali nel 2025 riflettono una convergenza di innovazione, supporto politico e domanda di mercato finale, con l’Asia-Pacifico che guida in volume e il Nord America e l’Europa che si concentrano su applicazioni specializzate e di alto valore.

Prospettive Future: Applicazioni Emergenti e Punti Caldi di Investimento

Le prospettive future per il packaging microelettronico con dies impilati nel 2025 sono plasmate da rapidi progressi nell’integrazione dei semiconduttori, dalla proliferazione dell’AI e del calcolo ad alte prestazioni, e dalla crescente domanda di sistemi elettronici miniaturizzati e ad alta densità. Il packaging con dies impilati, che prevede l’integrazione verticale di più chip semiconduttori all’interno di un unico pacchetto, è sempre più riconosciuto come un facilitatore chiave per dispositivi di nuova generazione in diversi settori ad alta crescita.

Le applicazioni emergenti sono particolarmente prominenti nei data center, nelle infrastrutture 5G e nel calcolo edge. La necessità di maggiore larghezza di banda e minore latenza in questi ambienti sta guidando l’adozione di architetture di dies impilati 2.5D e 3D, che offrono prestazioni elettriche migliorate e lunghezze di interconnessione ridotte. Nel 2025, ci si aspetta un’accelerazione dell’integrazione della memoria ad alta larghezza di banda (HBM) con i chip logici, a supporto delle esigenze computazionali di acceleratori AI e processori grafici avanzati. Aziende come Samsung Electronics e TSMC stanno investendo pesantemente in linee di packaging avanzato per soddisfare questa domanda.

Un’altra applicazione emergente è nel settore automotive, dove il packaging con dies impilati sta consentendo lo sviluppo di moduli compatti e ad alta affidabilità per sistemi avanzati di assistenza al conducente (ADAS) e veicoli autonomi. I requisiti rigorosi dell’industria automobilistica riguardanti la gestione termica e l’affidabilità stanno spingendo all’innovazione nelle tecnologie di packaging a livello di wafer (WLP) e vie attraverso il silicio (TSV), con fornitori come Infineon Technologies e NXP Semiconductors che espandono i loro portafogli per affrontare queste esigenze.

I punti caldi di investimento nel 2025 si prevede che si concentreranno sull’Asia-Pacifico, in particolare Taiwan, Corea del Sud e Cina, dove incentivi governativi e un robusto ecosistema di fonderie stanno accelerando R&D e l’espansione della capacità. Secondo Gartner, si prevede che il mercato globale del packaging avanzato crescerà con un CAGR di oltre il 7% fino al 2025, con le soluzioni di dies impilati che rappresentano una parte significativa di questa crescita. Il capitale di rischio e gli investimenti strategici stanno anche fluendo verso startup che sviluppano nuovi materiali di interconnessione e tecniche di integrazione eterogenea, come evidenziato dai recenti round di finanziamento tracciati da CB Insights.

- AI e HPC: Packaging con dies impilati per acceleratori AI e GPU

- Automotive: Moduli compatti ad alta affidabilità per ADAS e veicoli elettrici (EV)

- 5G/Edge: Soluzioni a bassa latenza e alta larghezza di banda per infrastrutture di rete

- Asia-Pacifico: Regione leader per investimenti e espansione della produzione

In sintesi, il 2025 vedrà il packaging microelettronico con dies impilati in prima linea nell’innovazione dei semiconduttori, con forte slancio in AI, automotive e comunicazioni, e significativa attività di investimento nell’Asia-Pacifico e nelle startup di materiali avanzati.

Sfide, Rischi e Opportunità Strategiche

Il packaging microelettronico con dies impilati, un pilastro dell’integrazione avanzata dei semiconduttori, affronta un paesaggio complesso di sfide e rischi nel 2025, ma presenta anche significative opportunità strategiche per gli attori del settore. La principale sfida tecnica rimane la gestione termica. Con un maggior numero di chips integrati verticalmente, la dissipazione del calore diventa sempre più problematica, rischiando l’affidabilità e la degradazione delle prestazioni dei dispositivi. Materiali interfaciali termici avanzati e innovativi design di dissipatori di calore sono in fase di esplorazione, ma la loro integrazione aggiunge costo e complessità al processo di produzione (SEMI).

I rischi di rendimento e affidabilità sono anche aumentati nelle architetture a dies impilati. Il numero crescente di interconnessioni, come le vie attraverso il silicio (TSV), aumenta la probabilità di difetti, influendo sul rendimento complessivo. Inoltre, l’integrazione eterogenea—combinando chip provenienti da diversi nodi di processo o fonderie—introduce sfide di compatibilità e testing. La necessità di strumenti avanzati di ispezione e metrologia sta crescendo, ma queste soluzioni possono aumentare significativamente i costi di capitale (TechInsights).

La complessità della catena di approvvigionamento è un altro rischio critico. Il packaging con dies impilati richiede spesso collaborazioni tra più fornitori per wafer, substrati e servizi di assemblaggio. Le interruzioni in qualsiasi segmento possono ritardare la produzione e aumentare i costi. Le tensioni geopolitiche e i controlli sulle esportazioni, in particolare nel commercio tecnologico tra Stati Uniti e Cina, aggravano ulteriormente le vulnerabilità della catena di approvvigionamento (Gartner).

Nonostante queste sfide, abbondano le opportunità strategiche. La domanda di calcolo ad alte prestazioni, acceleratori AI e dispositivi mobili avanzati sta guidando l’adozione rapida di soluzioni con dies impilati. Le aziende che investono in gestione termica proprietaria, testing avanzato e robuste strategie di catena di approvvigionamento possono differenziarsi e catturare segmenti di mercato premium. Inoltre, le partnership tra fonderie, OSAT (Assemblaggio e Test di Semiconduttori Esternalizzati) e fornitori EDA (Automazione della Progettazione Elettronica) stanno abilitando nuovi paradigmi di design e produzione, come le architetture basate su chiplet, che possono sbloccare ulteriore valore (TSMC).

- La gestione termica e l’affidabilità rimangono i principali ostacoli tecnici.

- La perdita di rendimento e i costi di ispezione stanno aumentando con la maggiore complessità dell’integrazione.

- I rischi della catena di approvvigionamento sono amplificati da fattori geopolitici e logistici.

- Investimenti strategici in R&D, partnership e resilienza della catena di approvvigionamento offrono vantaggi competitivi.

Fonti & Riferimenti

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights