2025 Stacked Die Mikroelektronikų Pakavimo Rinkos Ataskaita: Augimas, Technologiniai Pokyčiai ir Strateginės Įžvalgos Paskesniems 5 Metams. Išnagrinėkite Pagrindines Tendencijas, Prognozes ir Konkurencinę Dinamiką, Formuojančią Pramonę.

- Vykdomoji Santrauka ir Rinkos Apžvalga

- Pagrindinės Technologijų Tendencijos Stacked Die Mikroelektronikų Pakavime

- Konkurencinė Aplinka ir Pagrindiniai Žaidėjai

- Rinkos Augimo Prognozės (2025–2030): CAGR, Pajamų ir Tūrio Analizė

- Regioninė Rinkos Analizė: Šiaurės Amerika, Europa, Azija-Pacifikas ir Likusi Pasaulio Dalis

- Ateities Perspektyvos: Atsirandančios Programos ir Investicijų Centrai

- Iššūkiai, Rizikos ir Strateginės Galimybės

- Šaltiniai ir Nuorodos

Vykdomoji Santrauka ir Rinkos Apžvalga

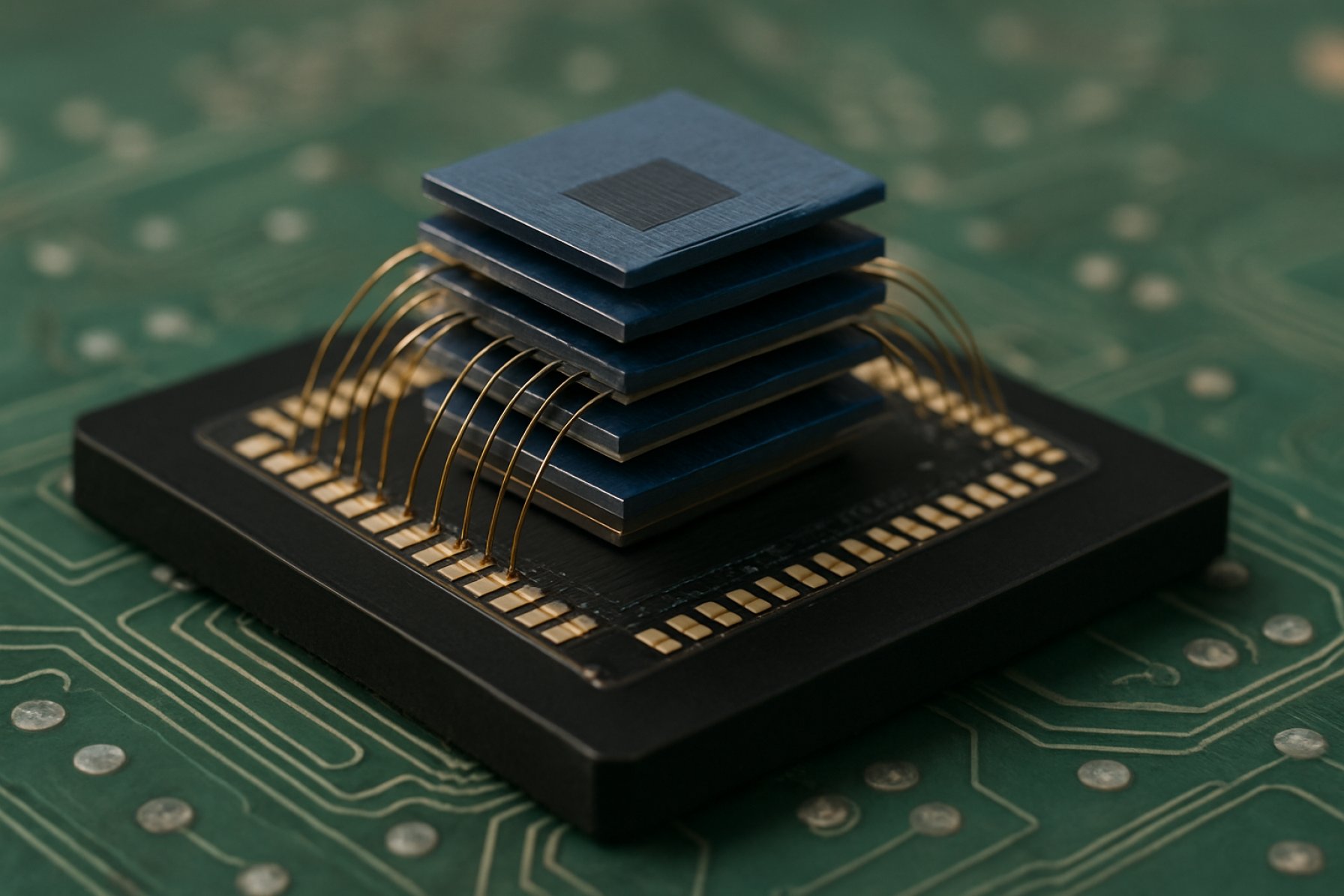

Stacked die mikroelektronikų pakavimas yra kelių puslaidininkių lustų integravimas į vieną paketą, išdėstytą vertikaliai, siekiant optimizuoti vietą, našumą ir funkcionalumą. Ši pažangi pakavimo technologija yra pagrindinė, norint patenkinti didėjančios miniatiūrizavimo, didesnio našumo ir energijos efektyvumo paklausą vartotojų elektronikos, automobilių, telekomunikacijų ir duomenų centrų sektoriuose. 2025 metų duomenimis, pasaulinė stacked die mikroelektronikų pakavimo rinka patiria tvirtą augimą, kurį įtakoja 5G įrenginių, dirbtinio intelekto (AI) programų ir Interneto dalykų (IoT) plitimas.

Pasak Gartner, stacked die pakavimo rinka prognozuojama, kad pasieks daugiau kaip 8% sudėtinį metinį augimo tempą (CAGR) 2023–2027 metų laikotarpiu, o pajamos iki 2025 metų turėtų viršyti 12 milijardų USD. Šis augimas remiasi vis didėjančiu 3D integruotųjų grandinių (3D ICs), sistemos pakete (SiP) sprendimų ir didelės juostos atminties (HBM) modulių, kurie visi naudoja stacked die architektūras, siekiant užtikrinti didesnį našumą ir sumažinti dydžio faktorius.

Pagrindiniai pramonės žaidėjai, tokie kaip TSMC, Samsung Electronics ir Intel Corporation, intensyviai investuoja į tyrimus ir plėtrą, kad tobulintų visos silicio jungtys (TSV) ir lustų lygio pakavimo (WLP) technologijas. Šios inovacijos leidžia didesnį tarpusavio ryšio tankį, geresnį šilumos valdymą ir mažesnę energijos sąnaudas, kas yra kritiškai svarbus naujos kartos programoms, tokioms kaip AI akceleratoriai, pažangios vairuotojo pagalbos sistemos (ADAS) ir aukšto našumo kompiuterija (HPC).

Regioniniu mastu Azija-Pacifikas dominuoja stacked die pakavimo rinkoje, užimanti daugiau kaip 60% pasaulinės gamybos pajėgumų, daugiausiai dėl pirmaujančių gamyklų ir OSAT (išorinių puslaidininkių surinkimo ir testavimo) teikėjų buvimo tokiose šalyse kaip Taivanas, Pietų Korėja ir Kinija. Šiaurės Amerika ir Europa taip pat stebi augančią paklausą, ypač automobilių elektronikoje ir duomenų centrų infrastruktūroje, kaip nurodo IC Insights.

Apibendrinant galima teigti, kad stacked die mikroelektronikų pakavimas yra labai svarbi technologija puslaidininkių pramonės evoliucijai 2025 metais, leidžianti didesnį integravimą, našumą ir efektyvumą įvairiose programose. Rinkos trajektoriją formuoja nuolatinis technologinis tobulėjimas, strateginės investicijos iš pirmaujančių žaidėjų ir nesibaigianti paklausa „protingesniems“, „mažesniems“ ir „galingesniems“ elektroniniams sistemoms.

Pagrindinės Technologijų Tendencijos Stacked Die Mikroelektronikų Pakavime

Stacked die mikroelektronikų pakavimas yra naujovių puslaidininkių srityje priešakyje, leidžiantis didesnį prietaisų našumą, padidintą funkcionalumą ir sumažintus dydžio faktorius vertikaliai integruojant kelis puslaidininkių lustus į vieną paketą. 2025 metais pramonė susiduria su keletu pagrindinių technologijų tendencijų, formuojančių stacked die pakavimo sprendimų evoliuciją ir priėmimą.

- Paprasta Technologija (TSV) Integracija: TSV technologija lieka vienu iš pagrindinių didelio tankio lustų gniuždymo. 2025 metais gamintojai tobulina TSV procesus, siekdami sumažinti vamzdžių diametrą ir žingsnį, todėl didėja tarpusavio ryšio tankis ir gerėja elektros našumas. Tai ypač svarbu aukšto našumo kompiuterijai (HPC) ir dirbtinio intelekto (AI) programoms, kur atminties juostos plotis yra kritinė problema. TSMC ir Samsung Electronics yra pirmaujantys komercinėje 2.5D ir 3D IC pakavimo TSV technologijų srityje.

- Hybrid Bonding Technologijos: Hibridinis ryšys, derinantis tiesioginį vario su vario ir dielektrinių su dielektriniais ryšiais, įgauna populiarumą kaip metodas, siekiant pasiekti ultra-smulkius tarpusavio ryšius ir patobulintas elektros charakteristikas. Ši technologija leidžia sub-10 mikronų žingsnį, būtinas kitai kartai logikos-atminties integracijai. Amkor Technology ir Intel Corporation paskelbė reikšmingus investicijas į hibridinį ryšį tiek atminties, tiek logikos įrenginiuose.

- Heterogeninė Integracija: Tendencija integruoti įvairius lustus – logikos, atminties, RF ir analoginius – į vieną stacked paketą didėja. Šis požiūris leidžia optimizuoti kiekvienos funkcijos proceso mazgus, pagerindamas bendrą sistemos našumą ir energijos efektyvumą. Pramonės asociacija SEMI akcentuoja heterogeninę integraciją kaip pagrindinį galimybę pažangios automobilių, 5G ir edge computing sprendimams.

- Šilumos Valdymo Inovacijos: Kuo didesnė lustų gniuždymo energijos tankumas, tuo labiau pažangūs šilumos sąsajų medžiagos (TIMs), mikrofluidinė aušinimo ir integruotos šilumos platintojai kuriami šilumos pašalinimui valdyti. Yole Group praneša, kad efektyvus šilumos valdymas dabar yra pagrindinis skirtumas stacked die paketo dizaino srityje, ypač duomenų centrams ir AI akceleratorių rinkai.

- Automatizuotas Testavimas ir Inspekcija: Stacked die surinkimų sudėtingumas reikalauja pažangių testavimo ir inspekto sprendimų, įskaitant aukštos raiškos rentgeno ir dirbtinio intelekto varomą gedimų aptikimą. KLA Corporation ir Teradyne plečia savo pasiūlą, kad spręstų unikalius daugelio lustų paketo patikimumo ir derliaus iššūkius.

Šios technologijų tendencijos bendrai skatina stacked die mikroelektronikų pakavimo rinką link didesnio integravimo, našumo ir patikimumo, pozicionuodamos ją kaip kritinį galimybę ateities elektroninėms sistemoms 2025 metais ir vėliau.

Konkurencinė Aplinka ir Pagrindiniai Žaidėjai

Stacked die mikroelektronikų pakavimo rinkos konkurencinė aplinka 2025 metais pasižymi intensyviomis inovacijomis, strateginiais partnerystėmis ir dėmesiu pažangiems gamybos gebėjimams. Šį sektorių skatina paklausa didesniam prietaisų našumui, miniatiūrizavimui ir integracijai tokiose programose kaip išmanieji telefonai, aukšto našumo kompiuterija, automobilių elektronika ir IoT įrenginiai. Pagrindiniai žaidėjai pasinaudoja savo patirtimi lustų lygio pakavimo, TSV technologijos ir heterogeninės integracijos srityse, kad išlaikytų konkurencinį pranašumą.

Rinką pirmauja įsitvirtinę puslaidininkių pakavimo ir surinkimo paslaugų teikėjai, tokie kaip Amkor Technology, ASE Technology Holding ir TSMC. Šios įmonės investavo dideles sumas į R&D ir gamybos pajėgumus, kad palaikytų didelio gamybos apimtis stacked die sprendimų srityje. Pavyzdžiui, TSMC pažangios CoWoS (Chip-on-Wafer-on-Substrate) ir SoIC (System on Integrated Chips) technologijos plačiai naudojamos aukštosios kompiuterijos ir AI programose, o Amkor Technology ir ASE Technology Holding siūlo plačią 2.5D ir 3D pakavimo paslaugų portfelį vartotojų ir verslo rinkoms.

IDM (integruotų prietaisų gamintojai), tokie kaip Intel Corporation ir Samsung Electronics, taip pat yra pastebimi, integruodami stacked die pakavimą į savo produktų plėtros planus, siekdami pagerinti lustų našumą ir energijos efektyvumą. Intel Foveros technologija ir Samsung X-Cube platforma iliustruoja nuosavus požiūrius į vertikalią integraciją ir chipletų architektūras.

Kylančios bendrovės ir nišinių specialistų, tokių kaip JCET Group ir Powertech Technology Inc., įgauna pagreitį siūlydamos pritaikytus sprendimus ir orientuodamosi į specifinius sektorius, tokius kaip automobilių ir pramoninė elektronika. Šios įmonės dažnai bendradarbiauja su fabless puslaidininkių įmonėmis ir sistemų integratoriais, kad pateiktų pritaikytus stacked die paketus.

Konkurencinė aplinka dar labiau formuojama nuolatinių M&A veiksmų, technologijų licencijavimo ir bendrų įmonių, kad įmonės galėtų plėsti savo galimybes ir pasaulinį pasiekiamumą. Pasak Yole Group, rinka tikimasi toliau konsoliduoti, o pirmaujančios įmonės investuos į naujos kartos tarpusavio ryšius, pažangias medžiagas ir automatizaciją, kad atitiktų nuolat besikeičiančius AI, 5G ir edge computing rinkos poreikius.

Rinkos Augimo Prognozės (2025–2030): CAGR, Pajamų ir Tūrio Analizė

Stacked die mikroelektronikų pakavimo rinka numatoma stipraus augimo 2025–2030 metų laikotarpiu, augant paklausai aukštos našumo, miniatiūrizuotų elektroninių prietaisų visose vartotojų elektronikos, automobilių ir duomenų centrų programose. Pasak MarketsandMarkets, pasaulinė 3D IC ir stacked die pakavimo rinka turėtų registruoti sudėtinį metinį augimo tempą (CAGR) apie 12% šiuo laikotarpiu. Ši augimo trajektorija remiasi vis didėjančiu pažangių pakavimo sprendimų priėmimu sprendžiant tradicinių 2D architektūrų apribojimus, ypač energijos efektyvumo, formos faktoriaus ir juostos pločio srityse.

Pajamų prognozės rodo, kad stacked die mikroelektronikų paketo segmentas 2030 metais viršys 15 milijardų USD, palyginti su 2025 metų prognozuojamomis 8.5 milijardų USD. Šis augimas yra priskiriamas dirbtinio intelekto (AI), 5G infrastruktūros ir edge computing plitimui, kurie visi reikalauja didesnio tarpusavio ryšio tankio ir geresnio šilumos valdymo – esminių pranašumų, kuriuos teikia stacked die architektūros. Gartner pabrėžia, kad puslaidininkių pramonės perėjimas prie heterogeninės integracijos ir sistemos pakete (SiP) sprendimų dar labiau pagreitins stacked die pakavimo technologijų priėmimą.

Kalbant apie tūrį, prognozuojama, kad stacked die vienetų, siunčiamų 2025–2030 metų laikotarpiu, skaičius augs 13–14% CAGR, atspindint tiek didesnį įsiskverbimą į didelių paklausų vartotojų įrenginius, tiek plečiamą naudojimą automobilių elektronikoje ir pramoniniame IoT. Yole Group praneša, kad pirmaujančios gamyklos ir OSAT(teikėjai) didina investicijas į pažangias pakavimo linijas, kad patenkintų šią didėjančią paklausą, o Azija-Pacifikas išlieka dominuojančiu gamybos centru dėl savo užsibrėžtos puslaidininkių gamybos ekosistemos.

- CAGR (2025–2030): 12–14%

- Pajamos (2030): USD 15+ milijardų

- Tūrio Augimas: Dėl vartotojų elektronikos, automobilių ir duomenų centrų taikymo

- Pagrindinės Regionai: Azija-Pacifikas pirmauja, sekama Šiaurės Amerikos ir Europos

Bendrai stacked die mikroelektronikų pakavimo rinka numatoma reikšmingai plėtojama, skatinama technologinių naujovių ir nuolatinio siekio didesnio našumo ir integracijos ateities elektroninėse sistemose.

Regioninė Rinkos Analizė: Šiaurės Amerika, Europa, Azija-Pacifikas ir Likusi Pasaulio Dalis

Pasaulinė stacked die mikroelektronikų pakavimo rinka patiria dinamišką augimą, o regioninės tendencijos formuojamos technologinėmis inovacijomis, galutinio vartotojo paklausa ir tiekimo grandinės plėtra. 2025 metais Šiaurės Amerika, Europa, Azija-Pacifikas ir likusi pasaulio dalis (RoW) kiekvienas pasižymi išskirtinėmis rinkos savybėmis ir augimo varikliais.

- Šiaurės Amerika: Šiaurės Amerikos rinka stimuliuojama tvirtų investicijų į pažangią puslaidininkių gamybą ir didelį pirmaujančių technologijų įmonių buvimą. Ši regionas naudoja didelius R&D veiksmus, ypač Jungtinėse Valstijose, kur stumimas dėl vidaus lustų gamybos yra remiamas vyriausybes iniciatyvų, tokių kaip CHIPS Aktas. Pagrindinės taikomosios sritys: aukšto našumo kompiuterija, automobilių elektronika ir gynybos sistemos. Pasak Puslaidininkių Pramonės Asociacijos, Šiaurės Amerika turėtų išlaikyti stabilų augimą stacked die pakavime, kai didėja paklausa miniatiūrizuotų, didelio tankio sprendimų AI ir 5G infrastruktūroje.

- Europa: Europos rinka pasižymi dėmesiu automobilių, pramoninės automatizacijos ir IoT programoms. Regiono orientacija į kokybę ir patikimumą, kartu su griežtomis reguliavimo standartais, skatina pažangių pakavimo technologijų priėmimą. Tokie projektai kaip Europos Lustų Aktas yra skirti stiprinti vietines puslaidininkių galimybes. Pasak SEMI, Europos gamintojai vis labiau investuoja į stacked die sprendimus, kad paremti besivystančią elektrinių automobilių ir išmaniosios gamybos sektorių.

- Azija-Pacifikas: Azija-Pacifikas dominuoja pasaulinėje stacked die mikroelektronikų pakavimo rinkoje, užimdama didžiausią dalį 2025 metais. Ši lyderystė remiasi didelėmis gamyklomis ir OSAT (išorinių puslaidininkių surinkimo ir testavimo) teikėjais, esančiais Tokijuje, Pietų Korėjoje, Kinijoje ir Japonijoje. Šio regiono didelis vartotojų elektronikos, išmaniųjų telefonų ir duomenų centrų priėmimas skatina didelio tankio pakavimą. Pasak IC Insights, azijos-pacifikos rinkos augimą dar labiau spartina vyriausybes paskatos ir agresyvūs pajėgumų plėtojimai iš pirmaujančių žaidėjų.

- Likusi Pasaulio Dalis (RoW): RoW segmentas, įskaitant Lotynų Ameriką, Vidurinius Rytus ir Afriką, išlieka naujas, tačiau turi potencialą augti, kai skaitmeninės transformacijos iniciatyvos plečiasi. Investicijos į telekomunikacijų infrastruktūrą ir besivystančius elektronikos gamybos centrus palaipsniui didins paklausą stacked die pakavimo sprendimams, kaip pastebi Gartner.

Bendras regioninis dinamizmas 2025 metais atspindi inovacijų, politikos paramos ir galutinės rinkos paklausos susikirtimą, kai Azija-Pacifikas pirmauja pagal tūrį, o Šiaurės Amerika ir Europa orientuojasi į didelės vertės, specializuotas programas.

Ateities Perspektyvos: Atsirandančios Programos ir Investicijų Centrai

Ateities perspektyvos stacked die mikroelektronikų pakavimui 2025 metais formuojamos greitų puslaidininkių integracijos pažangų, AI ir aukšto našumo kompiuterijos plitimo bei didėjančios paklausos miniatiūrizuotoms, didelio tankio elektroninėms sistemoms. Stacked die pakavimas, kuris apima vertikalią daugelio puslaidininkių lustų integraciją į vieną paketą, vis labiau pripažįstamas kaip pagrindinė galimybė tooke tikstant naujos kartos prietaisams daugelyje didelių augimo sektorių.

Atsirandančios programos ypač ryškios duomenų centruose, 5G infrastruktūroje ir edge computing. Didelių juostos plotų ir mažesnės vėlinimo sąnaudos šiose aplinkose skatina 2.5D ir 3D stacked die architektūrų priėmimą, kurios siūlo geresnį elektros našumą ir sumažintus tarpusavio ryšio ilgius. 2025 metais tikimasi, kad didelio juostos pločio atminties (HBM) ir logikos lustų integracija paspartės, remdama AI akceleratorių ir pažangių grafikos procesorių skaičiavimo reikmes. Tokios įmonės kaip Samsung Electronics ir TSMC intensyviai investuoja į pažangias pakavimo linijas, kad atitiktų šią paklausą.

Kita atsirandanti programa yra automobilių sektoriuje, kur stacked die pakavimas leidžia kurti kompaktiškus, aukštos patikimumo modulius pažangioms vairuotojo pagalbos sistemoms (ADAS) ir autonominiams automobiliams. Automobilių pramonės griežti reikalavimai šilumos valdymui ir patikimumui skatina inovacijas per silicio vyresnių metodų (TSV) ir lustų lygio pakavimo technologijose, o tiekėjai, tokie kaip Infineon Technologies ir NXP Semiconductors, plečia savo portfelių, kad atitiktų šiuos poreikius.

Investicijų centrai 2025 metais tikimasi koncentruotis Azija-Pacifikas, ypač Taivane, Pietų Korėjoje ir Kinijoje, kur vyriausybes paskatos ir tvirtos gamybos ekosistemos spartina R&D ir pajėgumų plėtros procesus. Pasak Gartner, pasaulinė pažangių pakavimo rinka prognozuojama, kad augs daugiau nei 7% CAGR iki 2025 metų, kur stacked die sprendimai sudarys reikšmingą šios plėtros dalį. Rizikingas kapitalas ir strateginės investicijos taip pat plečiasi į startuolius, kurie plėtoja naujus tarpusavio ryšio medžiagas ir heterogeninių integracijos technikas, kaip pažymėjo neseniai finansavimo raundai, stebimi CB Insights.

- AI ir HPC: Stacked die pakavimas AI akceleratoriams ir GPU

- Automobilių pramonė: Aukštos patikimumo, kompaktiški moduliai ADAS ir EV

- 5G/Edge: Mažos vėlinimo, didelio juostos pločio sprendimai tinklo infrastruktūrėms

- Azija-Pacifikas: Pirmaujanti regionas investicijoms ir gamybos plėtrai

Apibendrinant, 2025 metai bus metais, kai stacked die mikroelektronikų pakavimas bus technologijų innovacijų priešakyje, turint tvirtą pagreitį AI, automobilių ir komunikacijų srityse, bei įvykdant reikšmingas investicijas Azijoje-Pacifiką ir pažangių medžiagų startuolius.

Iššūkiai, Rizikos ir Strateginės Galimybės

Stacked die mikroelektronikų pakavimas, kaip pažangios puslaidininkių integracijos kertinis akmuo, 2025 metais susiduria su sudėtinga iššūkių ir rizikų aplinka, bet taip pat suteikia reikšmingas strategines galimybes pramonės žaidėjams. Pirmasis techninis iššūkis išlieka šilumos valdymas. Augant integruotų lustų skaičiui, šilumos šalinimas tampa vis problemas, todėl kyla rizika prietaisų patikimumui ir našumo pablogėjimui. Pažangios šilumos sąsajų medžiagos ir novatoriškų dizainų šilumos platinimo sprendimai yra tiriami, tačiau jų integracija didina gamybos sąnaudas ir sudėtingumą (SEMI).

Derlingumo ir patikimumo rizikos taip pat didėja stacked die architektūrose. Padidėjęs tarpusavio ryšio skaičius, pavyzdžiui, per silicio jungtis (TSVs), didina defekto tikimybę, diskredituodamos bendrą derlingumą. Be to, heterogeninė integracija – die skirtingų proceso mazgų arba gamyklų derinimas – sukelia suderinamumo ir testavimo iššūkius. Per šalies didinant pažangių inspekcijų ir metrologijos įrankių poreikis didėja, tačiau šie sprendimai gali ženkliai didinti kapitalo išlaidas (TechInsights).

Tiekimo grandinės sudėtingumas yra dar viena kritinė rizika. Stacked die pakavimas dažnai reikalauja bendradarbiauti su keliais tiekėjais pagal lustus, substratus ir surinkimo paslaugas. Bet koks sutrikimas bet kuriame segmente gali atidėti gamybą ir padidinti išlaidas. Geopolitikos įtampos ir eksporto kontrolės, ypač JAV-Kinijos technologijų prekybos kontekste, dar labiau pablogina tiekimo grandinės pažeidžiamumus (Gartner).

Nepaisant šių iššūkių, strateginės galimybės yra gausios. Paklausa aukštos našumo kompiuteriui, AI akceleratoriams ir pažangių mobilių įrenginių sprendimams skatina greitą stacked die sprendimų priėmimą. Įmonės, kurios investuoja į nuosavas šilumos valdymo, pažangias testavimo, ir patikimas tiekimo grandinės strategijas, gali skirtis savimi ir užimti aukštos vertės rinkos segments. Be to, teigiamas bendradarbiavimas tarp gamyklų, OSAT ir EDA (elektroninės projektavimo automatizacijos) tiekėjų leidžia kurti naujas dizaino ir gamybos paradigmas, tokių kaip chipletų architektūros, kurios gali dar labiau išlaisvinti vertę (TSMC).

- Šilumos valdymas ir patikimumas išlieka svarbiausi techniniai iššūkiai.

- Derliaus praradimai ir inspekcijos išlaidos didėja su didėjančia integracijos sudėtingumu.

- Tiekimo grandinės rizikos stiprinamos geopolitiniais ir logistiniais veiksniais.

- Strateginės investicijos į R&D, partnerystes ir tiekimo grandinės atsparumą teikia konkurencines pranašumus.

Šaltiniai ir Nuorodos

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Puslaidininkių Pramonės Asociacija

- Infineon Technologies

- NXP Semiconductors

- TechInsights