Raport na temat rynku pakowania mikroelektroniki w 2025 roku: Wzrost, zmiany technologiczne i strategiczne spostrzeżenia na następne 5 lat. Zbadaj kluczowe trendy, prognozy i dynamikę konkurencji kształtującą branżę.

- Streszczenie i przegląd rynku

- Kluczowe trendy technologiczne w pakowaniu mikroelektroniki z użyciem układów w stosie

- Krajobraz konkurencyjny i wiodący gracze

- Prognozy wzrostu rynku (2025–2030): CAGR, analiza przychodów i wolumenu

- Analiza rynku regionalnego: Ameryka Północna, Europa, Azja-Pacyfik i reszta świata

- Perspektywy na przyszłość: Nowe aplikacje i popularne miejsca inwestycyjne

- Wyzwania, ryzyka i strategiczne możliwości

- Źródła i odniesienia

Streszczenie i przegląd rynku

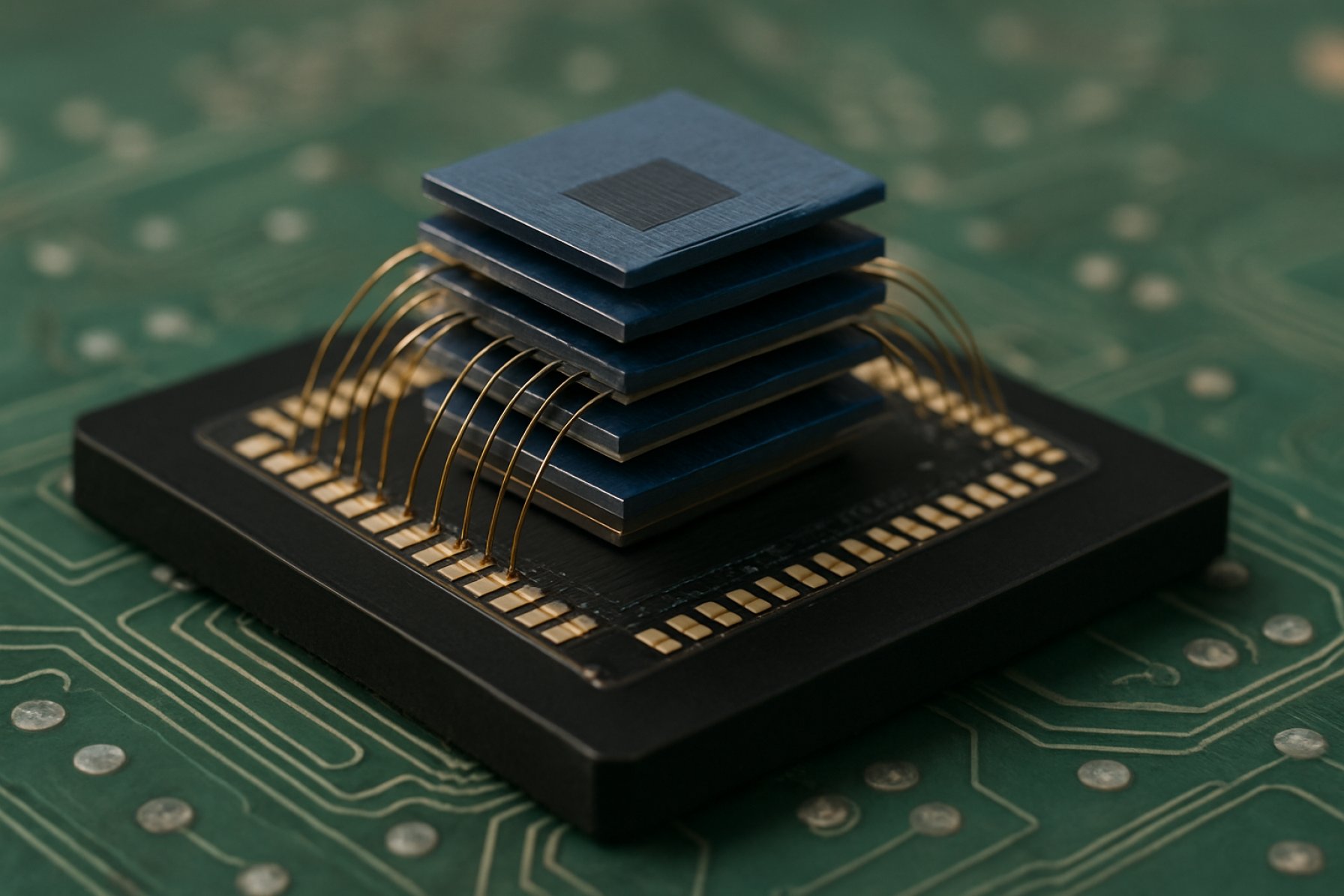

Pakowanie mikroelektroniki z użyciem układów w stosie odnosi się do integracji wielu układów półprzewodnikowych w jednej obudowie, ułożonych pionowo w celu optymalizacji przestrzeni, wydajności i funkcjonalności. Ta zaawansowana technologia pakowania odgrywa kluczową rolę w zaspokajaniu rosnących wymagań w zakresie miniaturyzacji, wyższej wydajności i efektywności energetycznej w takich sektorach jak elektronika użytkowa, motoryzacja, telekomunikacja i centra danych. W 2025 roku globalny rynek pakowania mikroelektroniki w układach w stosie doświadcza dynamicznego wzrostu, napędzanego powszechnym stosowaniem urządzeń 5G, aplikacji sztucznej inteligencji (AI) oraz Internetu Rzeczy (IoT).

Zgodnie z danymi Gartnera, rynek pakowania w stosie ma osiągnąć roczną stopę wzrostu (CAGR) przekraczającą 8% w latach 2023–2027, a przychody mają przekroczyć 12 miliardów dolarów do 2025 roku. Wzrost ten wspierany jest przez rosnące przyjęcie zintegrowanych obwodów 3D (3D IC), rozwiązań systemów w obudowie (SiP) oraz modułów pamięci o wysokiej szerokości pasma (HBM), które wykorzystują architektury układów w stosie, aby zapewnić lepszą wydajność i zmniejszyć rozmiary.

Kluczowe firmy w branży, takie jak TSMC, Samsung Electronics i Intel Corporation, intensywnie inwestują w badania i rozwój, aby doskonalić technologie przezsilikonowych połączeń (TSV) i pakowania na poziomie wafli (WLP). Te innowacje umożliwiają wyższą gęstość połączeń, poprawę zarządzania ciepłem oraz mniejsze zużycie energii, co jest krytyczne dla aplikacji nowej generacji w przyspieszaczach AI, zaawansowanych systemach wspomagania kierowcy (ADAS) i wysokowydajnym przetwarzaniu (HPC).

Regionalnie, Azja-Pacyfik dominuje na rynku pakowania w stosie, stanowiąc ponad 60% globalnej zdolności produkcyjnej, głównie dzięki obecności wiodących fabryk i dostawców OSAT (outsourced semiconductor assembly and test) w takich krajach jak Tajwan, Korea Południowa i Chiny. Ameryka Północna i Europa również obserwują rosnącą adopcję, szczególnie w elektronice motoryzacyjnej i infrastrukturze centrów danych, jak zauważa IC Insights.

Podsumowując, pakowanie mikroelektroniki w układach w stosie jest zasadniczą technologią dla ewolucji branży półprzewodnikowej w 2025 roku, umożliwiając wyższą integrację, wydajność i efektywność w szerokim zakresie zastosowań. Dynamika rynku kształtowana jest przez trwające postępy technologiczne, strategiczne inwestycje wiodących graczy oraz nieustającą potrzebę inteligentniejszych, mniejszych i mocniejszych systemów elektronicznych.

Kluczowe trendy technologiczne w pakowaniu mikroelektroniki z użyciem układów w stosie

Pakowanie mikroelektroniki w układach w stosie znajduje się na czołowej pozycji innowacji w dziedzinie półprzewodników, umożliwiając wyższą wydajność urządzeń, zwiększoną funkcjonalność i zmniejszone wymiary poprzez pionową integrację wielu układów półprzewodnikowych w jednej obudowie. W miarę jak branża zbliża się do 2025 roku, kilka kluczowych trendów technologicznych kształtuje ewolucję i adopcję rozwiązań pakowania w układach w stosie.

- Zaawansowana integracja przezsilikonowych połączeń (TSV): Technologia TSV pozostaje kamieniem węgielnym dla pakowania w wysokiej gęstości, oferując połączenia o niskim opóźnieniu i dużej przepustowości między pionowo wyrównanymi układami. W 2025 roku producenci udoskonalają procesy TSV, aby zmniejszyć średnicę i rozstaw połączeń, co zwiększa gęstość połączeń i poprawia wydajność elektryczną. Jest to szczególnie istotne dla aplikacji wysokowydajnego przetwarzania (HPC) i sztucznej inteligencji (AI), gdzie przepustowość pamięci stanowi wąskie gardło. TSMC i Samsung Electronics prowadzą prace nad komercjalizacją zaawansowanego pakowania IC 2,5D i 3D opartego na TSV.

- Techniki hybrydowego wiązania: Hybrydowe wiązanie, które łączy bezpośrednie wiązanie miedzi do miedzi oraz dielektryków do dielektryków, zyskuje na popularności jako metoda do osiągnięcia ultra-drobnych połączeń i poprawionych charakterystyk elektrycznych. Ta technologia umożliwia stosowanie układów w rozstawie poniżej 10 mikronów, co jest kluczowe dla integracji logiki z pamięcią nowej generacji. Amkor Technology i Intel Corporation ogłosiły znaczne inwestycje w hybrydowe wiązanie zarówno dla urządzeń pamięci, jak i logiki.

- Integracja heterogeniczna: Trend integracji różnych chipletów—takich jak logika, pamięć, RF i analogowe—w jedną pakietową strukturę w stosie przyspiesza. To podejście pozwala na optymalizację węzłów procesowych dla każdej funkcji, poprawiając ogólną wydajność systemu i efektywność energetyczną. Stowarzyszenie przemysłowe SEMI podkreśla integrację heterogeniczną jako kluczowy czynnik umożliwiający zaawansowane rozwiązania w samochodach, 5G i obliczeniach brzegowych.

- Innowacje w zarządzaniu ciepłem: W miarę wzrostu gęstości mocy w pakowaniu w stosie, opracowywane są zaawansowane materiały interfejsowe (TIM), mikrofluidyczne systemy chłodzenia i zintegrowane rozpraszacze ciepła, aby zarządzać odprowadzeniem ciepła. Grupa Yole raportuje, że skuteczne zarządzanie ciepłem staje się teraz kluczowym czynnikiem w projektowaniu pakietów w stosach, szczególnie w rynkach centrów danych i przyspieszaczy AI.

- Zautomatyzowane testowanie i inspekcja: Złożoność zespołów z układami w stosie wymaga zaawansowanych rozwiązań testowych i inspekcyjnych, w tym wysokorozdzielczej tomografii rentgenowskiej i wykrywania defektów napędzanego AI. KLA Corporation i Teradyne rozszerzają swoje oferty, aby sprostać unikalnym wyzwaniom związanym z niezawodnością pakietów multi-die i wydajnością.

Te trendy technologiczne wspólnie kierują rynkiem pakowania mikroelektroniki w układach w stosie ku większej integracji, wydajności i niezawodności, pozycjonując go jako krytyczny czynnik umożliwiający nowej generacji systemy elektroniczne w 2025 roku i później.

Krajobraz konkurencyjny i wiodący gracze

Krajobraz konkurencyjny rynku pakowania mikroelektroniki z użyciem układów w stosie w 2025 roku charakteryzuje się intensywną innowacją, strategicznymi partnerstwami i naciskiem na zaawansowane zdolności produkcyjne. Ten sektor jest napędzany przez popyt na wyższą wydajność urządzeń, miniaturyzację i integrację w takich zastosowaniach jak smartfony, wysokowydajne przetwarzanie, elektronika motoryzacyjna oraz urządzenia IoT. Kluczowi gracze wykorzystują swoją wiedzę w zakresie pakowania na poziomie wafli, technologii przezsilikonowych połączeń (TSV) i integracji heterogenicznej, aby utrzymać przewagę konkurencyjną.

Na czele rynku znajdują się ustalone firmy zajmujące się pakowaniem półprzewodników i usługami montażu, w tym Amkor Technology, ASE Technology Holding i TSMC. Firmy te zainwestowały znaczne środki w badania i rozwój oraz zdolności produkcyjne, aby wspierać produkcję w dużych ilościach rozwiązań w stosie. Na przykład zaawansowane technologie TSMC CoWoS (Chip-on-Wafer-on-Substrate) i SoIC (System on Integrated Chips) są szeroko stosowane w wysokowydajnych zastosowaniach obliczeniowych i AI, podczas gdy Amkor Technology i ASE Technology Holding oferują szeroki wachlarz usług pakowania 2,5D i 3D dla rynków konsumenckich i przedsiębiorstw.

IDM (Integrated Device Manufacturers), takich jak Intel Corporation i Samsung Electronics, również zajmują znaczącą pozycję, integrując pakowanie w stosie w swoje plany produktowe w celu zwiększenia wydajności chipów i efektywności energetycznej. Technologia Foveros Intela i platforma X-Cube Samsunga są przykładem proprietary podejścia do integracji pionowej i architektur opartych na chipletach.

Nowe firmy i niszowe specjalistyczne przedsiębiorstwa, w tym JCET Group i Powertech Technology Inc., zyskują na znaczeniu, oferując spersonalizowane rozwiązania i celując w konkretne sektory, takie jak elektronika motoryzacyjna i przemysłowa. Firmy te często współpracują z bezfabrycznymi firmami półprzewodnikowymi oraz integratorami systemów w celu dostarczenia dostosowanych pakietów w stosie.

Koniec środowiska konkurencyjnego jest dodatkowo kształtowany przez trwające działania fuzji i przejęć, licencjonowanie technologii oraz wspólne przedsięwzięcia, gdyż firmy dążą do rozszerzenia swoich zdolności i globalnego zasięgu. Według grupy Yole, rynek ma spodziewać się dalszej konsolidacji, z wiodącymi graczami inwestującymi w nowej generacji połączenia, zaawansowane materiały i automatyzację, aby sprostać zmieniającym się potrzebom rynków AI, 5G i obliczeń brzegowych.

Prognozy wzrostu rynku (2025–2030): CAGR, analiza przychodów i wolumenu

Rynek pakowania mikroelektroniki w układach w stosie jest gotowy na dynamiczny wzrost w latach 2025-2030, napędzany rosnącym popytem na wysokowydajne, miniaturowe urządzenia elektroniczne w zastosowaniach elektroniki użytkowej, motoryzacji i centrów danych. Zgodnie z prognozami MarketsandMarkets, globalny rynek 3D IC i pakowania w układach w stosie ma zarejestrować roczną stopę wzrostu (CAGR) wynoszącą około 12% w tym okresie. Ta trajektoria wzrostu opiera się na rosnącym przyjęciu zaawansowanych rozwiązań pakowania, aby zaspokoić ograniczenia tradycyjnych architektur 2D, szczególnie w kontekście efektywności energetycznej, formatu i przepustowości.

Prognozy dotyczące przychodów wskazują, że segment pakowania mikroelektroniki w układach w stosie przekroczy 15 miliardów USD do 2030 roku, w porównaniu do oszacowanych 8,5 miliarda dolarów w 2025 roku. Ten wzrost przypisywany jest powszechnemu zastosowaniu sztucznej inteligencji (AI), infrastruktury 5G oraz obliczeń brzegowych, które wymagają wyższej gęstości połączeń oraz lepszego zarządzania ciepłem—kluczowych zalet oferowanych przez architektury układów w stosie. Gartner podkreśla, że przemysł półprzewodnikowy przekształca się w kierunku integracji heterogenicznej i rozwiązań systemów w obudowie (SiP), co dodatkowo przyspieszy adopcję technologii pakowania w układach w stosie.

W kontekście ilości, liczba jednostek układów w stosie wysłanych na rynek ma rosnąć w tempie CAGR wynoszącym 13–14% w latach 2025-2030, co odzwierciedla zarówno wzrost penetracji w urządzeniach konsumpcyjnych o dużych wolumenach, jak i rozszerzone zastosowania w elektronice motoryzacyjnej i przemyśle IoT. Grupa Yole raportuje, że wiodące fabryki i OSAT (Zewnętrzne usługi montażu i testowania półprzewodników) zwiększają inwestycje w zaawansowane linie pakujące, aby sprostać oczekiwanemu zapotrzebowaniu, przy czym Azja-Pacyfik pozostaje dominującym hubem produkcyjnym z uwagi na rozwiniętą ekosystem półprzewodników.

- CAGR (2025–2030): 12–14%

- Przychody (2030): Powyżej 15 miliardów USD

- Wzrost wolumenu: Napędzany przez elektronikę konsumpcyjną, motoryzację i zastosowania centrów danych

- Kluczowe regiony: Azja-Pacyfik prowadzi, w ślad za Ameryką Północną i Europą

Ogólnie rzecz biorąc, rynek pakowania mikroelektroniki w układach w stosie jest gotowy na znaczny rozwój, napędzany innowacjami technologicznymi i nieustannym dążeniem do wyższej wydajności i integracji w systemach elektronicznych nowej generacji.

Analiza rynku regionalnego: Ameryka Północna, Europa, Azja-Pacyfik i reszta świata

Globalny rynek pakowania mikroelektroniki w układach w stosie doświadcza dynamicznego wzrostu, przy czym trendy regionalne kształtowane są przez innowacje technologiczne, popyt użytkowników i rozwój łańcucha dostaw. W 2025 roku rynki Ameryki Północnej, Europy, Azji-Pacyfiku i reszty świata (RoW) prezentują różne cechy rynku i czynniki wzrostu.

- Ameryka Północna: Rynek północnoamerykański jest napędzany solidnymi inwestycjami w zaawansowaną produkcję półprzewodników oraz silnym obecnością wiodących firm technologicznych. Region korzysta z znaczących działań badawczo-rozwojowych, szczególnie w Stanach Zjednoczonych, gdzie dążenie do krajowej produkcji chipów wspierane jest przez inicjatywy rządowe takie jak ustawa CHIPS. Kluczowe zastosowania obejmują wysokowydajne przetwarzanie, elektronikę motoryzacyjną i systemy obronne. Według Stowarzyszenia Przemysłu Półprzewodnikowego, Ameryka Północna ma utrzymać stabilny wzrost w pakowaniu w układach w stosie, napędzany popytem na miniaturowe, rozwiązania o wysokiej gęstości w AI i infrastrukturze 5G.

- Europa: Rynek europejski charakteryzuje się mocnym skupieniem na aplikacjach motoryzacyjnych, automatyce przemysłowej i IoT. Nacisk regionu na jakość i niezawodność, w połączeniu z rygorystycznymi normami regulacyjnymi, sprzyja adopcji zaawansowanych technologii pakowania. Inicjatywy takie jak europejska ustawa o chipach mają na celu wzmocnienie lokalnych zdolności w zakresie półprzewodników. Według SEMI, europejscy producenci coraz bardziej inwestują w rozwiązania w układach w stosie, aby wspierać rozwijający się w regionie sektor pojazdów elektrycznych i inteligentnej produkcji.

- Azja-Pacyfik: Azja-Pacyfik dominuje na globalnym rynku pakowania mikroelektroniki w układach w stosie, stanowiąc największy udział w 2025 roku. Ta dominacja opiera się na obecności głównych fabryk i dostawców OSAT w krajach takich jak Tajwan, Korea Południowa, Chiny i Japonia. Szybka adopcja elektroniki użytkowej, smartfonów i centrów danych w regionie napędza popyt na pakowanie o wysokiej gęstości. Zgodnie z raportem IC Insights, rozwój rynku Azji-Pacyfiku jest dodatkowo wspierany przez zachęty rządowe oraz agresywne rozszerzenia zdolności przez wiodące firmy.

- Reszta świata (RoW): Segment RoW, obejmujący Amerykę Łacińską, Bliski Wschód i Afrykę, pozostaje w początkowej fazie rozwoju, ale wykazuje potencjał wzrostu w miarę rozszerzania się inicjatyw transformacji cyfrowej. Inwestycje w infrastrukturę telekomunikacyjną i rozwijające się ośrodki produkcji elektroniki mają stopniowo zwiększać popyt na rozwiązania pakowania w układach w stosie, jak zauważa Gartner.

Ogólnie rzecz biorąc, dynamika regionalna w 2025 roku odzwierciedla konwergencję innowacji, wsparcia politycznego oraz popytu na rynku końcowym, przy czym Azja-Pacyfik prowadzi pod względem wielkości, a Ameryka Północna i Europa skupiają się na unikających wartościowych, wyspecjalizowanych zastosowaniach.

Perspektywy na przyszłość: Nowe aplikacje i popularne miejsca inwestycyjne

Perspektywy na przyszłość dla pakowania mikroelektroniki w 2025 roku kształtowane są przez szybkie postępy w integracji półprzewodników, powszechne stosowanie AI i wysokowydajnych systemów obliczeniowych oraz rosnący popyt na miniaturowe, o wysokiej gęstości systemy elektroniczne. Pakowanie w układach w stosie, polegające na pionowej integracji wielu układów półprzewodnikowych w jednej obudowie, jest coraz bardziej uznawane za kluczowy czynnik umożliwiający nowej generacji urządzenia w kilku sektorach o wysokim wzroście.

Nowe aplikacje wyraźnie pojawiają się w centrach danych, infrastrukturze 5G i obliczeniach brzegowych. Potrzeba wyższej przepustowości i niższych opóźnień w tych środowiskach napędza adopcję architektur układów w 2,5D i 3D, które oferują poprawioną wydajność elektryczną i skrócone długości połączeń. W 2025 roku spodziewana jest przyspieszona integracja pamięci o wysokiej szerokości pasma (HBM) z układami logicznymi, co wspiera wymagania obliczeniowe przyspieszaczy AI i zaawansowanych procesorów graficznych. Firmy takie jak Samsung Electronics i TSMC intensywnie inwestują w zaawansowane linie pakujące, aby sprostać temu zapotrzebowaniu.

Inną wschodzącą aplikacją jest sektor motoryzacyjny, w którym pakowanie w układach w stosie umożliwia opracowywanie kompaktowych, niezawodnych modułów dla zaawansowanych systemów wspomagania kierowcy (ADAS) oraz samochodów autonomicznych. Rygorystyczne wymagania przemysłu motoryzacyjnego dotyczące zarządzania ciepłem i niezawodności pobudzają innowacje w technologii TSV i pakowania waflowego, z dostawcami takimi jak Infineon Technologies i NXP Semiconductors, rozszerzającym swoje portfele, aby sprostać tym potrzebom.

Miejsca inwestycyjne w 2025 roku mają koncentrować się wokół Azji-Pacyfiku, szczególnie Tajwanu, Korei Południowej i Chin, gdzie zachęty rządowe i silne ekosystemy fabryczne przyspieszają działalność badawczo-rozwojową oraz rozwój zdolności produkcyjnych. Zgodnie z przewidywaniami Gartnera, globalny rynek zaawansowanego pakowania ma rosnąć w tempie CAGR przekraczającym 7% do 2025 roku, a rozwiązania w układach w stosie stanowią znaczny udział w tym wzroście. Kapitał venture i strategiczne inwestycje również płyną do startupów rozwijających nowatorskie materiały połączeniowe i techniki integracji heterogenicznej, co podkreślają ostatnie rundy finansowania, które śledzi CB Insights.

- AI i HPC: Pakowanie w układach w stosie dla przyspieszaczy AI i GPU

- Motoryzacja: Niezawodne, kompaktowe moduły dla ADAS i EV

- 5G/Brzeg: Rozwiązania o niskim opóźnieniu i dużej przepustowości dla infrastruktury sieciowej

- Azja-Pacyfik: Wiodący region inwestycji i rozwoju produkcji

Podsumowując, w 2025 roku pakowanie mikroelektroniki w układach w stosie znajdzie się na czołowej pozycji w innowacjach półprzewodnikowych, z silnym momentum w obszarach AI, motoryzacji i komunikacji oraz znaczną aktywnością inwestycyjną w Azji-Pacyfiku i startupach zajmujących się materiałami zaawansowanymi.

Wyzwania, ryzyka i strategiczne możliwości

Pakowanie mikroelektroniki w układach w stosie, będące fundamentem zaawansowanej integracji półprzewodników, napotyka złożony krajobraz wyzwań i ryzyk w 2025 roku, ale także stwarza znaczne strategiczne możliwości dla graczy w branży. Głównym wyzwaniem technicznym pozostaje zarządzanie ciepłem. Wraz z pionową integracją większej liczby układów, odprowadzanie ciepła staje się coraz bardziej problematyczne, co zagraża niezawodności urządzeń i może prowadzić do pogorszenia ich wydajności. Badane są zaawansowane materiały interfejsowe i innowacyjne projekty rozpraszaczy ciepła, jednak ich integracja zwiększa koszty i złożoność procesu produkcyjnego (SEMI).

Ryzyko wydajności i niezawodności również wzrasta w architekturach z układami w stosie. Zwiększona liczba połączeń, takich jak przezsilikonowe połączenia (TSV), podnosi prawdopodobieństwo wystąpienia defektów, co wpływa na ogólną wydajność. Ponadto integracja heterogeniczna—łączenie układów z różnych węzłów procesowych lub fabryk—wprowadza wyzwania dotyczące kompatybilności i testowania. Potrzeba nowoczesnych narzędzi inspekcji i metrologii rośnie, ale tego typu rozwiązania mogą znacznie zwiększyć wydatki kapitałowe (TechInsights).

Złożoność łańcucha dostaw to kolejne istotne ryzyko. Pakowanie w układach w stosie często wymaga współpracy między wieloma dostawcami dla wafli, podłoży i usług montażowych. Zakłócenia w dowolnym segmencie mogą opóźnić produkcję i zwiększyć koszty. Napięcia geopolityczne i kontrola eksportu, szczególnie w handlu technologicznym pomiędzy USA a Chinami, dodatkowo pogłębiają wrażliwość łańcucha dostaw (Gartner).

Pomimo tych wyzwań istnieją znaczne możliwości strategiczne. Popyt na wysokowydajne przetwarzanie, przyspieszacze AI i zaawansowane urządzenia mobilne napędza szybkie przyjęcie rozwiązań w pakowaniu w układach w stosie. Firmy, które inwestują w własne technologie zarządzania ciepłem, zaawansowane testowanie oraz solidne strategie zarządzania łańcuchem dostaw mogą się wyróżnić i zająć czołowe segmenty rynku. Dodatkowo partnerstwa między fabrykami, OSAT (Zewnętrznymi usługami montażu i testowania) oraz dostawcami EDA (Automatyzacja projektowania elektronicznego) umożliwiają nowe paradygmaty projektowania i produkcji, takie jak architektury oparte na chipletach, co dodatkowo może zwiększyć wartość (TSMC).

- Zarządzanie ciepłem i niezawodność pozostają głównymi wyzwaniami technicznymi.

- Straty w wydajności i koszty inspekcji rosną wraz z zwiększoną złożonością integracji.

- Ryzyka w łańcuchu dostaw są potęgowane przez czynniki geopolityczne i logistyczne.

- Strategiczne inwestycje w badania i rozwój, partnerstwa oraz odporność łańcucha dostaw oferują przewagi konkurencyjne.

Źródła i odniesienia

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Stowarzyszenie Przemysłu Półprzewodnikowego

- Infineon Technologies

- NXP Semiconductors

- TechInsights