Raportul Pieței Ambalajelor Microelectronice cu Die Stacked 2025: Creștere, Schimbări Tehnologice și Perspective Strategice pentru Următorii 5 Ani. Explorați Tendințele Cheie, Proiecțiile și Dinamica Competitivă care Modelează Industria.

- Sumar Executiv & Prezentare Generală a Pieței

- Tendințe Tehnologice Cheie în Ambalajele Microelectronice cu Die Stacked

- Peisaj Competitiv și Jucători Importanți

- Proiecții de Creștere a Pieței (2025–2030): CAGR, Analiza Veniturilor și a Volumului

- Analiza Pieței Regionale: America de Nord, Europa, Asia-Pacific și Restul Lumii

- Perspective Viitoare: Aplicații Emergente și Puncte Focalizare pentru Investiții

- Provocări, Riscuri și Oportunități Strategice

- Surse & Referințe

Sumar Executiv & Prezentare Generală a Pieței

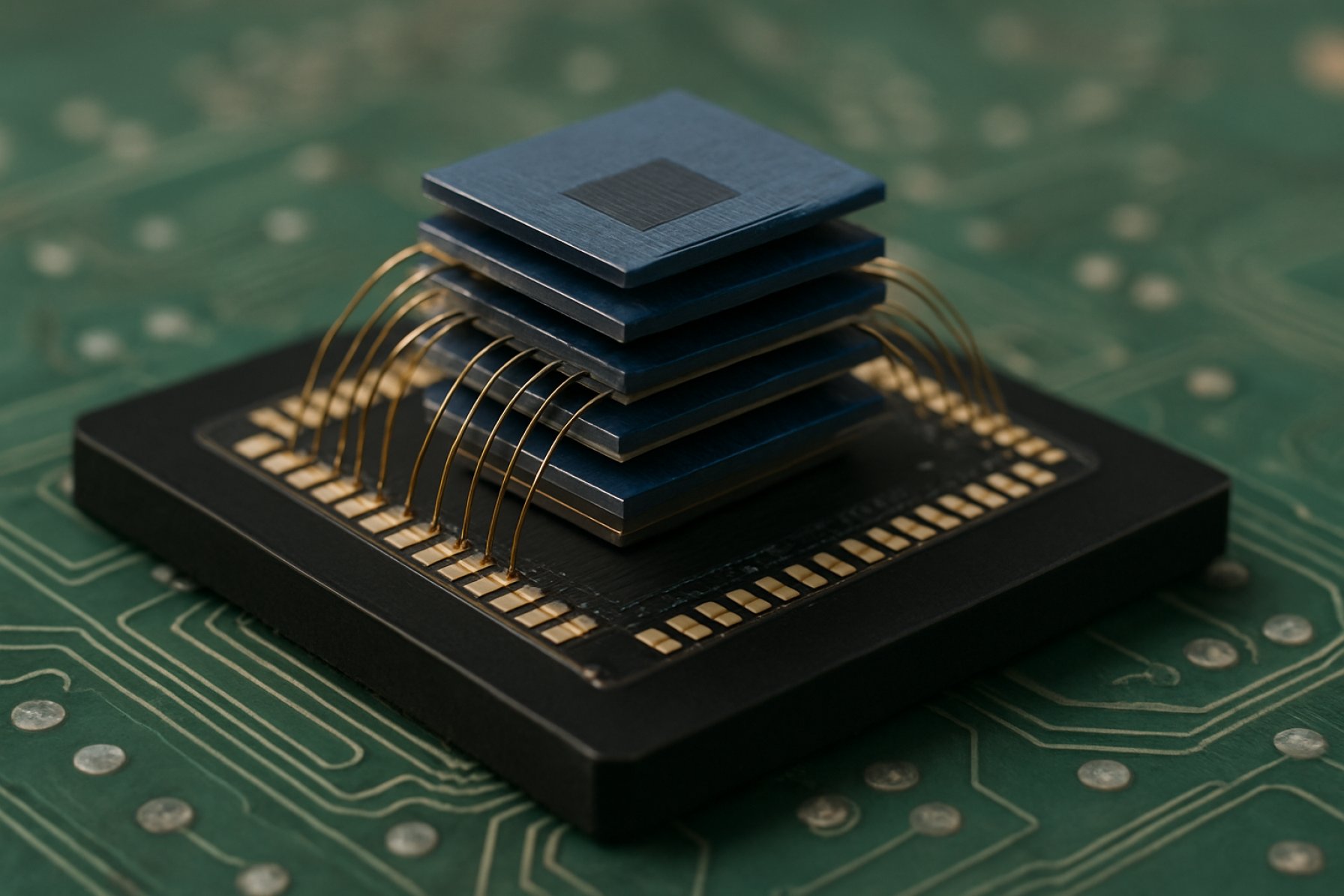

Ambalajele microelectronice cu die stacked se referă la integrarea mai multor die-uri semiconductoare într-un singur pachet, aranjate vertical pentru a optimiza spațiul, performanța și funcționalitatea. Această tehnologie avansată de ambalare este esențială pentru a răspunde cerințelor tot mai mari pentru miniaturizare, performanță mai ridicată și eficiență energetică în sectoare precum electronica de consum, automotive, telecomunicații și centrele de date. În 2025, piața globală pentru ambalajele microelectronice cu die stacked se bucură de o creștere robustă, alimentată de proliferarea dispozitivelor 5G, aplicațiilor inteligenței artificiale (AI) și Internetului Lucrurilor (IoT).

Conform Gartner, piața ambalajelor cu die stacked este prevăzută a atinge o rată anuală de creștere compusă (CAGR) de peste 8% între 2023 și 2027, cu venituri preconizate să depășească 12 miliarde de dolari până în 2025. Această creștere este susținută de adoptarea tot mai mare a circuitelor integrate 3D (3D IC), soluțiilor system-in-package (SiP) și modulelor de memorie cu lățime de bandă mare (HBM), toate acestea fiind concepute pentru a oferi performanțe îmbunătățite și forme reduse.

Jucători importanți din industrie, precum TSMC, Samsung Electronics și Intel Corporation, investesc masiv în cercetare și dezvoltare pentru a avansa tehnologiile de viață prin siliciu (TSV) și ambalarea la nivel de wafer (WLP). Aceste inovații permit densități de interconectare mai mari, o gestionare termică îmbunătățită și un consum de energie mai redus, esențiale pentru aplicațiile de generație următoare, cum ar fi acceleratorii AI, sistemele avansate de asistență pentru șoferi (ADAS) și calculul de înaltă performanță (HPC).

Din punct de vedere regional, Asia-Pacific domină piața ambalajelor cu die stacked, reprezentând mai mult de 60% din capacitatea de producție globală, în mare parte datorită prezenței celor mai importante fabrici și furnizori de OSAT (asmblare și testare semiconductor externe) în țări precum Taiwan, Coreea de Sud și China. America de Nord și Europa observă, de asemenea, o adoptare crescută, în special în electronica automotive și infrastructura centrelor de date, așa cum este menționat de IC Insights.

În concluzie, ambalajele microelectronice cu die stacked reprezintă o tehnologie fundamentală pentru evoluția industriei semiconductoarelor în 2025, permițând o integrare mai mare, performanță și eficiență într-o gamă largă de aplicații. Traiectoria pieței este modelată de progresele tehnologice continue, investițiile strategice ale jucătorilor de frunte și cererea neîncetată pentru sisteme electronice mai inteligente, mai mici și mai puternice.

Tendințe Tehnologice Cheie în Ambalajele Microelectronice cu Die Stacked

Ambalajele microelectronice cu die stacked se află în fruntea inovației semiconductoare, permițând o performanță mai mare a dispozitivelor, funcționalitate crescută și forme reduse prin integrarea verticală a mai multor die-uri semiconductoare într-un singur pachet. Pe măsură ce industria se îndreaptă spre 2025, mai multe tendințe tehnologice cheie modelează evoluția și adoptarea soluțiilor de ambalare cu die stacked.

- Integrarea Avansată prin Via Siliciu (TSV): Tehnologia TSV rămâne un element de bază pentru stivuirea de die-uri cu densitate mare, oferind interconexiuni cu latență redusă și lățimi de bandă mari între die-uri aliniate vertical. În 2025, producătorii îmbunătățesc procesele TSV pentru a reduce diametrul și pasul via, crescând astfel densitatea interconectării și îmbunătățind performanța electrică. Acest lucru este deosebit de critic pentru aplicațiile de calcul de înaltă performanță (HPC) și inteligență artificială (AI), unde lățimea de bandă a memoriei este o problemă. TSMC și Samsung Electronics conduc în comercializarea ambalării avansate bazate pe TSV 2.5D și 3D.

- Tehnici de Legare Hibridă: Legarea hibridă, care combină legarea directă cu cupru la cupru și dielectric la dielectric, câștigă teren ca metodă de a obține interconexiuni cu pas ultra-mic și caracteristici electrice îmbunătățite. Această tehnologie permite stivuirea cu pas sub 10 micrometri, ceea ce este esențial pentru integrarea logică-memorie de generație următoare. Amkor Technology și Intel Corporation au anunțat investiții semnificative în legarea hibridă atât pentru dispozitivele de memorie, cât și pentru cele logice.

- Integrarea Heterogenă: Tendința de a integra diverse chiplete—cum ar fi logic, memorie, RF și analogic—într-un pachet stivuit unic accelerează. Această abordare permite noduri de proces optimizate pentru fiecare funcție, îmbunătățind performanța sistemului general și eficiența energetică. Asociația industrială SEMI subliniază integrarea heterogenă ca un factor cheie pentru soluțiile avansate de automotive, 5G și calculul la margine.

- Inovații în Managementul Termic: Pe măsură ce stivuirea die-urilor crește densitatea de putere, materiale avansate de interfață termică (TIM), răcirea microfluidică și disipatoarele de căldură integrate sunt dezvoltate pentru a gestiona disiparea căldurii. Yole Group raportează că o gestionare eficientă a căldurii este acum un diferențiator principal în designul pachetelor cu die stacked, în special pentru piețele centrelor de date și acceleratorilor AI.

- Teste și Inspecție Automatizate: Complexitatea asamblărilor cu die stacked necesită soluții avansate de testare și inspecție, inclusiv raze X cu înaltă rezoluție și detectarea defectelor bazată pe AI. KLA Corporation și Teradyne își extind ofertele pentru a aborda provocările unice ale fiabilității și randamentului pachetelor multi-die.

Aceste tendințe tehnologice contribuie în mod colectiv la îmbunătățirea pieței ambalajelor microelectronice cu die stacked în direcția unei integrări, performanțe și fiabilități mai mari, poziționând-o ca un factor critic pentru sistemele electronice de generație următoare în 2025 și nu numai.

Peisaj Competitiv și Jucători Importanți

Peisajul competitiv al pieței ambalajelor microelectronice cu die stacked în 2025 este caracterizat prin inovație intensă, parteneriate strategice și un focus pe capacitățile avansate de producție. Acest sector este alimentat de cererea de performanță mai mare a dispozitivelor, miniaturizare și integrare în aplicații precum smartphone-uri, calculatoare de înaltă performanță, electronica automotive și dispozitive IoT. Jucătorii cheie își valorifică expertiza în ambalarea la nivel de wafer, tehnologia TSV și integrarea heterogenă pentru a-și menține un avantaj competitiv.

Conducând piața sunt furnizorii bine stabiliți de servicii de ambalare și asamblare a semiconductoarelor, inclusiv Amkor Technology, ASE Technology Holding și TSMC. Aceste companii au făcut investiții semnificative în R&D și capacitatea de producție pentru a susține fabricarea de înaltă volum pentru soluțiile de die stacked. De exemplu, tehnologiile avansate CoWoS (Chip-on-Wafer-on-Substrate) și SoIC (System on Integrated Chips) de la TSMC sunt adoptate pe scară largă pentru computația de înaltă performanță și aplicații AI, în timp ce Amkor Technology și ASE Technology Holding oferă un portofoliu extins de servicii de ambalare 2.5D și 3D pentru piețele de consum și întreprinderi.

IDM-urile (Integrated Device Manufacturers), cum ar fi Intel Corporation și Samsung Electronics, sunt de asemenea proeminente, integrând ambalajele cu die stacked în planurile lor de produse pentru a îmbunătăți performanța chipului și eficiența energetică. Tehnologia Foveros de la Intel și platforma X-Cube de la Samsung exemplifică abordările proprietare pentru integrarea verticală și arhitecturile bazate pe chiplete.

Jucatorii emergenți și specialiștii de nișă, inclusiv JCET Group și Powertech Technology Inc., câștigă teren prin oferirea de soluții personalizate și targetarea unor verticale specifice precum electronica automotive și industrială. Aceste companii colaborează adesea cu firme semiconductoare fără fabrici și integratori de sisteme pentru a livra pachete de die stacked adaptate.

Mediul competitiv este, de asemenea, modelat de activitatea continuă de fuzionare și achiziție, licențiere tehnologică și joint venture-uri, pe măsură ce companiile caută să-și extindă capacitățile și acoperirea globală. Conform Yole Group, piața se așteaptă să vadă o consolidare continuă, cu jucătorii de frunte investind în interconexiuni de generație următoare, materiale avansate și automatizare pentru a răspunde nevoilor în evoluție ale piețelor AI, 5G și de calcul la margine.

Proiecții de Creștere a Pieței (2025–2030): CAGR, Analiza Veniturilor și a Volumului

Piața ambalajelor microelectronice cu die stacked este pregătită pentru o creștere robustă între 2025 și 2030, alimentată de cererea în continuă creștere pentru dispozitive electronice de înaltă performanță și miniaturizate în aplicații de electronică de consum, automotive și centre de date. Conform proiecțiilor realizate de MarketsandMarkets, piața globală pentru IC-uri 3D și ambalaje cu die stacked este de așteptat să înregistreze o rată anuală de creștere compusă (CAGR) de aproximativ 12% în această perioadă. Această traiectorie de creștere este susținută de adoptarea tot mai mare a soluțiilor de ambalare avansate pentru a aborda limitările arhitecturilor tradiționale 2D, în special în ceea ce privește eficiența energetică, factorul de formă și lățimea de bandă.

Proiecțiile veniturilor indică faptul că segmentul ambalajelor microelectronice cu die stacked va depăși 15 miliarde USD până în 2030, în creștere de la aproximativ 8,5 miliarde USD în 2025. Această creștere este atribuită proliferării inteligenței artificiale (AI), infrastructurii 5G și calculului la margine, toate având nevoie de o densitate mai mare a interconectării și gestionare termică îmbunătățită—avantaje cheie oferite de arhitecturile cu die stacked. Gartner subliniază că trecerea industriei semiconductoarelor către integrarea heterogenă și soluțiile system-in-package (SiP) va accelera în continuare adoptarea tehnologiilor de ambalare cu die stacked.

În ceea ce privește volumul, numărul de unități de die stacked livrate este preconizat să crească cu o CAGR de 13–14% din 2025 până în 2030, reflectând atât penetrarea crescută în dispozitivele de consum cu volum mare, cât și utilizarea extinsă în electronica automotive și IoT industrial. Yole Group raportează că fabricile și OSAT-urile (furnizorii externi de asamblare și testare a semiconductorilor) de top își intensifică investițiile în linii de ambalare avansate pentru a răspunde acestei cereri anticipate, Asia-Pacific rămânând centrul de producție dominant datorită ecosistemului său stabilit de fabricație a semiconductoarelor.

- CAGR (2025–2030): 12–14%

- Venituri (2030): 15+ miliarde USD

- Cresterea Volumului: Alimentată de electronica de consum, automotive și aplicații de centre de date

- Regiuni Cheie: Asia-Pacific conduce, urmată de America de Nord și Europa

În general, piața ambalajelor microelectronice cu die stacked este pregătită pentru o expansiune semnificativă, impulsionată de inovația tehnologică și de presiunea neîncetată de a obține o performanță și integrare superioară în sistemele electronice de generație următoare.

Analiza Pieței Regionale: America de Nord, Europa, Asia-Pacific și Restul Lumii

Piața globală pentru ambalajele microelectronice cu die stacked se bucură de o creștere dinamică, cu tendințe regionale modelate de inovația tehnologică, cererea utilizatorilor finali și dezvoltările din lanțul de aprovizionare. În 2025, piețele din America de Nord, Europa, Asia-Pacific și Restul Lumii (RoW) prezintă fiecare caracteristici și motoare de creștere distincte.

- America de Nord: Piața nord-americană este impulsionată de investiții robuste în fabricația avansată de semiconductoare și prezența puternică a companiilor tehnologice de vârf. Regiunea beneficiază de activități semnificative de R&D, în special în Statele Unite, unde inițiativa pentru producția internă de cipuri este susținută de inițiative guvernamentale precum Legea CHIPS. Aplicațiile cheie includ calculul de înaltă performanță, electronica automotive și sistemele de apărare. Conform Asociației Industriei Semiconductoarelor, America de Nord se așteaptă să mențină o creștere constantă în ambalarea cu die stacked, alimentată de cererea pentru soluții miniaturizate și de densitate mare în infrastructura AI și 5G.

- Europa: Piața din Europa este caracterizată printr-un focus pe aplicații automotive, automatizare industrială și IoT. Accentul regiunii pe calitate și fiabilitate, alături de standardele de reglementare stricte, favorizează adoptarea tehnologiilor avansate de ambalare. Inițiative precum Legea Europeană a Cipurilor urmăresc consolidarea capabilităților locale în domeniul semiconductorilor. Conform SEMI, producătorii europeni investesc din ce în ce mai mult în soluții de die stacked pentru a susține sectorul în creștere al vehiculelor electrice și al producției inteligente.

- Asia-Pacific: Asia-Pacific domină piața globală de ambalaje microelectronice cu die stacked, având cea mai mare cotă în 2025. Această conducere este susținută de prezența fabricilor majore și a furnizorilor de OSAT în țări precum Taiwan, Coreea de Sud, China și Japonia. Adoptarea rapidă a electronicelor de consum, smartphone-urilor și centrelor de date din regiune stimulează cererea pentru ambalaje de densitate mare. Conform IC Insights, creșterea pieței din Asia-Pacific este accelerată și de stimulentele guvernamentale și de extinderea agresivă a capacităților de către jucătorii de frunte.

- Restul Lumii (RoW): Segmentul RoW, care include America Latină, Orientul Mijlociu și Africa, rămâne inițial, dar arată potențial de creștere pe măsură ce inițiativele de transformare digitală se extind. Investițiile în infrastructura de telecomunicații și centrele emergente de fabricație electronică sunt așteptate să crească treptat cererea pentru soluții de ambalare cu die stacked, așa cum subliniază Gartner.

În general, dinamica regională din 2025 reflectă o convergență a inovației, sprijinului politic și cererii de pe piața finală, cu Asia-Pacific conducând în volum și America de Nord și Europa concentrându-se pe aplicații specializate și de mare valoare.

Perspective Viitoare: Aplicații Emergente și Puncte Focalizare pentru Investiții

Perspectivele viitoare pentru ambalajele microelectronice cu die stacked în 2025 sunt modelate de avansuri rapide în integrarea semiconductorilor, proliferarea AI și a calculului de înaltă performanță, precum și de cererea în creștere pentru sisteme electronice miniaturizate și de densitate mare. Ambalajele cu die stacked, care implică integrarea verticală a mai multor die-uri semiconductoare într-un singur pachet, sunt din ce în ce mai recunoscute ca un facilitant cheie pentru dispozitivele de generație următoare în diverse sectoare cu creștere rapidă.

Aplicațiile emergente sunt deosebit de proeminente în centrele de date, infrastructura 5G și calculul la margine. Nevoia de lățimi de bandă mai mari și de latență mai mică în aceste medii determină adoptarea arhitecturilor cu die stacked 2.5D și 3D, care oferă performanțe electrice îmbunătățite și lungimi de interconectare reduse. În 2025, integrarea memoriei cu lățime de bandă mare (HBM) cu die-urile logice este de așteptat să se accelereze, susținând cerințele computaționale ale acceleratorilor AI și procesorilor grafici avansați. Companii precum Samsung Electronics și TSMC investesc masiv în linii avansate de ambalare pentru a răspunde acestei cereri.

O altă aplicație emergentă este în sectorul automotive, unde ambalajele cu die stacked facilitează dezvoltarea modulelor compacte și de înaltă fiabilitate pentru sistemele avansate de asistență pentru șoferi (ADAS) și vehiculele autonome. Cerințele stricte ale industriei auto pentru gestionarea termică și fiabilitate stimulează inovația în tehnologiile de viață prin siliciu (TSV) și ambalarea la nivel de wafer, cu furnizori precum Infineon Technologies și NXP Semiconductors extinzându-și portofoliile pentru a răspunde acestor nevoi.

Punctele focale pentru investiții în 2025 se așteaptă să se concentreze în jurul Asia-Pacific, în special Taiwan, Coreea de Sud și China, unde stimulentele guvernamentale și ecosistemele de fabrică robuste accelerează R&D și extinderea capacității. Conform Gartner, piața globală de ambalare avansată este proiectată să crească cu o CAGR de peste 7% până în 2025, cu soluțiile de die stacked reprezentând o parte semnificativă din această creștere. Capitalul de risc și investițiile strategice curg, de asemenea, către startup-uri care dezvoltă materiale interconectate inovatoare și tehnici de integrare heterogenă, așa cum evidențiază runde recente de finanțare monitorizate de CB Insights.

- AI și HPC: Ambalaje cu die stacked pentru acceleratorii AI și GPU-uri

- Automotive: Module compacte, de înaltă fiabilitate pentru ADAS și vehicule electrice

- 5G/Edge: Soluții de latență redusă și lățimi de bandă mari pentru infrastructura de rețea

- Asia-Pacific: Regiunea principală pentru investiții și expansiune a producției

În concluzie, 2025 va vedea ambalajele microelectronice cu die stacked în fruntea inovației semiconductoare, cu un impuls puternic în AI, automotive și comunicații, și activitate semnificativă de investiții în Asia-Pacific și în startup-uri de materiale avansate.

Provocări, Riscuri și Oportunități Strategice

Ambalajele microelectronice cu die stacked, un element de bază al integrării avansate a semiconductorilor, se confruntă cu un peisaj complex de provocări și riscuri în 2025, dar prezintă de asemenea oportunități strategice semnificative pentru jucătorii din industrie. Prima provocare tehnică rămâne gestionarea termică. Pe măsură ce mai multe die-uri sunt integrate vertical, disiparea căldurii devine din ce în ce mai problematică, riscând fiabilitatea și degradarea performanței dispozitivelor. Materialele avansate de interfață termică și conceptele inovative de disipare a căldurii sunt explorate, dar integrarea acestora adaugă costuri și complexitate procesului de fabricație (SEMI).

Riscurile privind randamentul și fiabilitatea sunt, de asemenea, amplificate în arhitecturile cu die stacked. Numărul crescut de interconectări, cum ar fi via-urile prin siliciu (TSV), cresc probabilitatea defectelor, afectând randamentul general. În plus, integrarea heterogenă—combinarea die-urilor din diferite noduri de proces sau fabrici—introduce provocări de compatibilitate și testare. Necesitatea unor instrumente avansate de inspecție și măsurare crește, dar aceste soluții pot crește semnificativ cheltuielile de capital (TechInsights).

Complexitatea lanțului de aprovizionare este un alt risc critic. Ambalarea cu die stacked necesită adesea colaborarea între furnizori multipli pentru wafere, substraturi și servicii de asamblare. Perturbările în orice segment pot întârzia producția și pot crește costurile. Tensiunile geopolitice și controalele la export, în special în comerțul cu tehnologie dintre SUA și China, agravează vulnerabilitățile lanțului de aprovizionare (Gartner).

În ciuda acestor provocări, oportunitățile strategice sunt abundente. Cererea pentru calcul de înaltă performanță, acceleratorii AI și dispozitivele mobile avansate determină o adoptare rapidă a soluțiilor cu die stacked. Companiile care investesc în gestionarea termică proprietară, teste avansate și strategii robuste de lanț de aprovizionare se pot diferenția și pot captura segmente de piață premium. În plus, parteneriatele dintre fabrici, OSAT-uri (Outsourced Semiconductor Assembly and Test) și furnizorii EDA (Electronic Design Automation) facilitează noi paradigme de design și fabricație, cum ar fi arhitecturile bazate pe chiplete, care pot debloca și mai mult valoare (TSMC).

- Gestionarea termică și fiabilitatea rămân principale provocări tehnice.

- Costurile de pierdere a randamentului și inspecție cresc odată cu complexitatea integrării.

- Riscurile din lanțul de aprovizionare sunt amplificate de factori geopolitici și logistici.

- Investițiile strategice în R&D, parteneriate și reziliența lanțului de aprovizionare oferă avantaje competitive.

Surse & Referințe

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Asociația Industriei Semiconductoarelor

- Infineon Technologies

- NXP Semiconductors

- TechInsights