Poročilo o trgu mikroelektronike zložene chipe 2025: Rast, tehnološke spremembe in strateški vpogledi za naslednjih 5 let. Raziščite ključne trende, napovedi in konkurenčne dinamike, ki oblikujejo industrijo.

- Izvršni povzetek in pregled trga

- Ključni tehnološki trendi v pakiranju zloženih čipov mikroelektronike

- Konkurenčno okolje in vodilni akterji

- Napovedi rasti trga (2025–2030): CAGR, analiza prihodkov in volumnov

- Analiza regionalnega trga: Severna Amerika, Evropa, Azijsko-pacifiška regija in preostali svet

- Prihodnji obeti: Priljubljene aplikacije in investicijska središča

- Izzivi, tveganja in strateške priložnosti

- Viri in reference

Izvršni povzetek in pregled trga

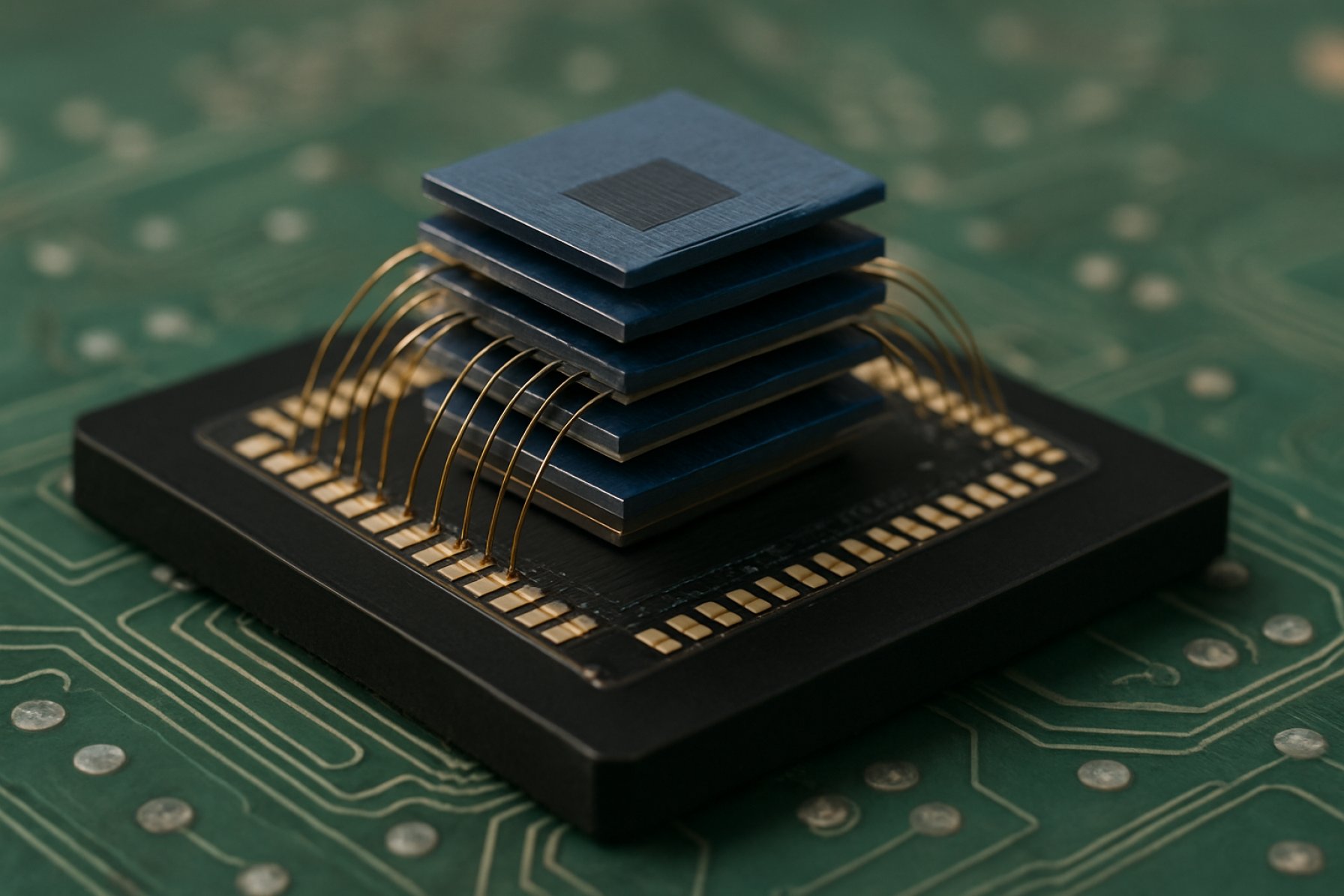

Pakiranje mikroelektronike zloženih čipov se nanaša na integracijo več polprevodniških čipov znotraj enega paketa, razporejenih vertikalno, da optimizirajo prostor, zmogljivost in funkcionalnost. Ta napredna tehnologija pakiranja je ključna pri izpolnjevanju naraščajočih zahtev po miniaturizaciji, višji zmogljivosti in energetski učinkovitosti v sektorjih, kot so potrošna elektronika, avtomobilizem, telekomunikacije in podatkovni centri. Do leta 2025 globalni trg pakiranja mikroelektronike z zloženimi čipi doživlja robustno rast, ki jo spodbuja proliferacija naprav 5G, aplikacij umetne inteligence (UI) in Interneta stvari (IoT).

Po napovedih podjetja Gartner bo trg pakiranja zloženih čipov dosegel letno stopnjo rasti (CAGR) več kot 8 % med letoma 2023 in 2027, pri čemer se pričakuje, da bodo prihodki presegli 12 milijard dolarjev do leta 2025. To rast podpira naraščajoča sprejetost 3D integreiranih vezij (3D IC), rešitev sistem-v-paketu (SiP) in modulov z visoko prepustnostjo spomina (HBM), ki vsi izkoriščajo arhitekture zloženih čipov za dosego izboljšane zmogljivosti in zmanjšanih dimenzij.

Ključni industrijski akterji, kot so TSMC, Samsung Electronics in Intel Corporation, močno vlagajo v raziskave in razvoj, da bi napredovali v tehnologijah preko-silikonskih povezav (TSV) in pakiranja na nivoju wafra (WLP). Te inovacije omogočajo višje gostote povezav, izboljšano upravljanje s toploto in manjšo porabo energije, kar je ključno za aplikacije naslednje generacije v pospeševalnikih UI, naprednih sistemih za pomoč pri vožnji (ADAS) in superračunalništvu (HPC).

Regionalno, Azijsko-pacifiška regija prevladuje na trgu pakiranja zloženih čipov, ki predstavlja več kot 60 % globalne proizvodne zmogljivosti, predvsem zaradi prisotnosti vodilnih livarni in OSAT (outsourced semiconductor assembly and test) ponudnikov v državah, kot so Tajvan, Južna Koreja in Kitajska. Severna Amerika in Evropa prav tako opažata povečano sprejetje, zlasti v avtomobilski elektroniki in infrastrukturi podatkovnih centrov, kot navaja IC Insights.

V povzetku, pakiranje mikroelektronike zloženih čipov je temeljna tehnologija za evolucijo industrije polprevodnikov v letu 2025, ki omogoča višjo integracijo, zmogljivost in učinkovitost v širokem spektru aplikacij. Rasti trga botrujejo stalni tehnološki napredki, strateške naložbe vodilnih akterjev in neizprosna povpraševanja po pametnejših, manjših in bolj zmogljivih elektronskih sistemih.

Ključni tehnološki trendi v pakiranju zloženih čipov mikroelektronike

Pakiranje mikroelektronike zloženih čipov je na čelu inovacij v industriji polprevodnikov in omogoča višjo zmogljivost naprav, povečano funkcionalnost in zmanjšane dimenzije z vertikalno integracijo več polprevodniških čipov znotraj enega paketa. Ko se industrija seli v leto 2025, več ključnih tehnoloških trendov oblikuje evolucijo in sprejetje rešitev za pakiranje zloženih čipov.

- Napredna integracija preko-silikonskih povezav (TSV): Tehnologija TSV ostaja temelj za zgoščeno zlaganje čipov, saj ponuja nizkoodločne, visoke pasovne povezave med vertikalno poravnanimi čipi. Leta 2025 proizvajalci izboljšujejo postopke TSV, da bi zmanjšali premer in razmik povezav, kar povečuje gostoto povezav in izboljšuje električno zmogljivost. To je še posebej kritično za superračunalništvo (HPC) in aplikacije umetne inteligence (UI), kjer je pasovna širina spomina ožji prostor. TSMC in Samsung Electronics vodita prizadevanja za komercializacijo naprednega pakiranja IC 2.5D in 3D na osnovi TSV.

- Tehnike hibridnega vezanja: Hibridno vezanje, ki združuje neposredno vezanje bakra na baker ter dielektrično vezanje na dielektrik, pridobiva na pomenu kot način za dosego ultra-finega razmika povezav ter izboljšanih električnih lastnosti. Ta tehnologija omogoča zlaganje pod 10 mikronov, kar je ključno za integracijo logike in spomina naslednje generacije. Amkor Technology in Intel Corporation sta napovedala pomembne naložbe v hibridno vezanje za naprave spomina in logike.

- Heterogena integracija: Trend integracije različnih čipov – kot so logika, spomin, RF in analogno – znotraj enega zloženega paketa se pospešuje. Ta pristop omogoča optimizacijo procesnih vozlišč za vsako funkcijo in izboljšanje splošne zmogljivosti sistema in energetske učinkovitosti. Združenje SEMI poudarja heterogeno integracijo kot ključni omogočitelj za napredne avtomobilske, 5G in rešitve obrobnega računalništva.

- Inovacije v upravljanju s toploto: Ker se gostota moči pri zlaganju čipov povečuje, se razvijajo napredni toplotni vmesni materiali (TIM), mikrofluidno hlajenje in integrirane toplotne razpršilnike za upravljanje disipacije toplote. Skupina Yole poroča, da je učinkovito upravljanje s toploto zdaj glavni diferencijski dejavnik pri oblikovanju paketov zloženih čipov, zlasti na trgih podatkovnih centrov in pospeševalnikov UI.

- Avtomatizirani testi in inšpekcija: Kompleksnost sestavkov zloženih čipov zahteva napredne rešitve za testiranje in inšpekcijo, vključno z visoko ločljivostjo rentgenskim slikanjem in z umetno inteligenco podprto odkrivanje napak. KLA Corporation in Teradyne širita svoje ponudbe, da bi se spoprijeli z edinstvenimi izzivi zanesljivosti in donosa veččipnih paketov.

Ti tehnološki trendi skupno usmerjajo trg pakiranja mikroelektronike zloženih čipov proti večji integraciji, zmogljivosti in zanesljivosti, kar ga postavlja za ključnega omogočevalca za elektronske sisteme naslednje generacije v letu 2025 in naprej.

Konkurenčno okolje in vodilni akterji

Konkurenčno okolje trga pakiranja mikroelektronike zloženih čipov v letu 2025 zaznamuje intenzivna inovacija, strateška partnerstva in osredotočenost na napredne proizvodne zmogljivosti. Ta sektor je usmerjen v zahteve po višji zmogljivosti naprav, miniaturizaciji in integraciji v aplikacijah, kot so pametni telefoni, superračunalništvo, avtomobilska elektronika in naprave IoT. Ključni igralci izkoriščajo svoje znanje na področju pakiranja na nivoju wafra, tehnologije preko-silikonskih povezav (TSV) in heterogene integracije, da ohranijo konkurenčno prednost.

Na trgu vodijo uveljavljeni ponudniki storitev pakiranja in sestavljanja polprevodnikov, kot so Amkor Technology, ASE Technology Holding in TSMC. Ta podjetja so naredila pomembne naložbe v R&D in proizvodne zmogljivosti za podporo visokovolumski proizvodnji rešitev zloženih čipov. Na primer, napredne tehnologije TSMC CoWoS (Chip-on-Wafer-on-Substrate) in SoIC (System on Integrated Chips) so široko sprejete za vrhunsko računalništvo in aplikacije UI, medtem ko Amkor Technology in ASE Technology Holding ponujata široko paleto storitev pakiranja 2.5D in 3D za potrošniške in podjetniške trge.

IDM (Integrated Device Manufacturers), kot sta Intel Corporation in Samsung Electronics, sta prav tako izstopajoča, integrirajoč pakiranje zloženih čipov v svoje načrte izdelkov, da bi izboljšali zmogljivost čipov in energetsko učinkovitost. Intelova tehnologija Foveros in Samsungova platforma X-Cube ponazarjata lastniške pristope k vertikalni integraciji in arhitekturama na osnovi čipov.

Novi igralci in specializirane naložbe, vključno z JCET Group in Powertech Technology Inc., pridobivajo na pomenu s ponujanjem prilagojenih rešitev in usmeritvijo na specifične vertikale, kot so avtomobilska in industrijska elektronika. Ta podjetja pogosto sodelujejo s podjetji brez livarn in integratorji sistemov, da dostavijo prilagojene pakete zloženih čipov.

Konkurenčno okolje dodatno oblikujejo kontinuirane aktivnosti združitev in prevzema, licenciranje tehnologij in skupna podjetja, saj podjetja iščejo možnosti za širitev svojih zmogljivosti in globalnega dosega. Po navedbah skupine Yole se pričakuje, da bo trg še naprej videl konsolidacijo, z vodilnimi igralci, ki vlagajo v naslednje generacije povezav, napredne materiale in avtomatizacijo, s ciljem odgovoriti na spreminjajoče se potrebe trgov umetne inteligence, 5G in obrobnega računalništva.

Napovedi rasti trga (2025–2030): CAGR, analiza prihodkov in volumnov

Trg pakiranja mikroelektronike zloženih čipov se pripravlja na robustno rast med letoma 2025 in 2030, podprt z naraščajočim povpraševanjem po visokozmogljivih, miniaturiziranih elektronskih napravah v potrošniški elektroniki, avtomobilizmu in aplikacijah podatkovnih centrov. Po napovedih MarketsandMarkets se pričakuje, da bo globalni trg 3D IC in pakiranja zloženih čipov registriral letno stopnjo rasti (CAGR) približno 12 % v tem obdobju. Ta rastna pot se podpira s povečanjem sprejetja naprednih rešitev pakiranja za reševanje omejitev tradicionalnih 2D arhitektur, zlasti glede energetske učinkovitosti, dimenzij in pasovne širine.

Napovedi prihodkov kažejo, da bo segment pakiranja mikroelektronike zloženih čipov presegla 15 milijard USD do leta 2030, kar je povečanje s približnih 8,5 milijard USD v letu 2025. Ta izjemen porast je pripisan proliferaciji umetne inteligence (UI), infrastrukture 5G in obrobnega računalništva, ki vse zahtevajo višjo gostoto povezav in izboljšano upravljanje s toploto – ključne prednosti, ki jih nudijo arhitekture zloženih čipov. Gartner poudarja, da bo prehod industrije polprevodnikov na heterogeno integracijo in rešitve sistem-v-paketu (SiP) dodatno pospešil sprejetje tehnologij pakiranja zloženih čipov.

Kar zadeva volumen, se pričakuje, da se bo število enot zloženih čipov, ki se pošljejo, povečalo s CAGR 13–14 % od 2025 do 2030, kar odraža tako povečano prodornost v visokovolumenskih potrošniških napravah kot tudi širšo uporabo v avtomobilski elektroniki in industrijskem IoT. Skupina Yole poroča, da vodilne livarne in OSAT (Outsourced Semiconductor Assembly and Test) podjetja povečujejo naložbe v napredne linije pakiranja, da bi zadovoljile to pričakovano povpraševanje, pri čemer azijsko-pacifiška regija ostaja prevladujoče proizvodno središče zaradi ustanovljenega ekosistema proizvodnje polprevodnikov.

- CAGR (2025–2030): 12–14%

- Prihodki (2030): USD 15+ milijard

- Rast volumna: Podprta s potrošniško elektroniko, avtomobilizmom in aplikacijami podatkovnih centrov

- Ključne regije: Azijsko-pacifiška regija vodi, sledita ji Severna Amerika in Evropa

Na splošno se trg pakiranja mikroelektronike zloženih čipov pripravlja na pomembno širitev, ki jo spodbuja tehnološka inovacija in neizprosna težnja po višji zmogljivosti in integraciji v elektronskih sistemih naslednje generacije.

Analiza regionalnega trga: Severna Amerika, Evropa, Azijsko-pacifiška regija in preostali svet

Globalni trg pakiranja mikroelektronike zloženih čipov doživlja dinamično rast, pri čemer so regionalni trendi oblikovani z inovacijami v tehnologiji, povpraševanjem končnih uporabnikov in razvojem dobavne verige. Leta 2025 bo vsak od regij Severne Amerike, Evrope, Azijski pacifik in preostali svet (RoW) predstavil posebne značilnosti trga in gonilne sile rasti.

- Severna Amerika: Trg Severne Amerike spodbuja močno vlaganje v napredne proizvodnje polprevodnikov in močna prisotnost vodilnih tehnoloških podjetij. Regija koristi od pomembnih dejavnosti R&D, zlasti v ZDA, kjer je pritisk za domačo proizvodnjo čipov podprt z vladnimi pobudami, kot je zakon CHIPS. Ključne aplikacije vključujejo superračunalništvo, avtomobilsko elektroniko in obrambo. Po informacijah Semiconductor Industry Association naj bi Severna Amerika ohranila stabilno rast v pakiranju zloženih čipov, kar je spodbudila povpraševanja po miniaturiziranih, visokogostotnih rešitvah v infrastrukturnih rešitvah UI in 5G.

- Evropa: Trg Evrope se odlikuje z osredotočenjem na avtomobilske, industrijske avtomatizacije in IoT aplikacije. Poudarek regije na kakovosti in zanesljivosti, skupaj z strogimi regulativnimi standardi, spodbuja sprejetje naprednih tehnologij pakiranja. Pobude, kot je Evropski zakon o čipih, si prizadevajo okrepiti lokalne zmogljivosti polprevodnikov. Po navedbah podjetja SEMI evropski proizvajalci vse bolj vlagajo v rešitve zloženih čipov, da bi podprli rastočo industrijo električnih vozil in pametne proizvodnje v regiji.

- Azijsko-pacifiška regija: Azijsko-pacifiška regija prevladuje na globalnem trgu pakiranja mikroelektronike zloženih čipov in bo leta 2025 zasedla največji delež. Ta vodilni položaj je podprt s prisotnostjo glavnih livarn in OSAT (Outsourced Semiconductor Assembly and Test) ponudnikov v državah, kot so Tajvan, Južna Koreja, Kitajska in Japonska. Hitro prilagajanje potrošniške elektronike, pametnih telefonov in podatkovnih centrov v regiji spodbuja povpraševanje po visokogostotnem pakiranju. Po navedbah IC Insights se rast trga Azijsko-pacifiške regije dodatno pospešuje s podpori vlade in agresivnim povečevanjem zmogljivosti vodilnih akterjev.

- Preostali svet (RoW): Segment RoW, ki vključuje Latinsko Ameriko, Srednji Vzhod in Afriko, ostaja v začetni fazi, a kaže potencial za rast, saj se širijo pobude digitalne transformacije. Naložbe v telekomunikacijsko infrastrukturo in nastajajoče elektronike proizvodne središča naj bi postopoma povečale povpraševanje po rešitvah pakiranja zloženih čipov, kot navaja Gartner.

Na splošno regijske dinamike v letu 2025 odražajo konvergenco inovacij, podpore politik in povpraševanja na trgu, pri čemer Azijsko-pacifiška regija vodi po volumnu, Severna Amerika in Evropa pa se osredotočata na visoko vrednostne, specializirane aplikacije.

Prihodnji obeti: Priljubljene aplikacije in investicijska središča

Prihodnji obeti za pakiranje mikroelektronike zloženih čipov v letu 2025 so oblikovani s hitrimi napredki v integraciji polprevodnikov, proliferacijo UI in superračunalništva ter naraščajočim povpraševanjem po miniaturiziranih, visokogostotnih elektronskih sistemih. Pakiranje zloženih čipov, ki vključuje vertikalno integracijo več polprevodniških čipov v en paket, se vse bolj prepoznava kot ključni omogočitelj za naprave naslednje generacije v več visokorastnih sektorjih.

Nove aplikacije so še posebej opazne v podatkovnih centrih, infrastrukturi 5G in obrobnem računalništvu. Potreba po višji pasovni širini in nižji zakasnitev v teh okoljih spodbuja sprejetje arhitektur 2.5D in 3D zloženih čipov, ki ponujajo izboljšano električno zmogljivost in zmanjšane dolžine povezav. Leta 2025 naj bi se integracija visoko pasovne spomina (HBM) z logičnimi čipi pospešila, kar bo podprlo računalniške zahteve UI pospeševalnikov in naprednih grafičnih procesorjev. Podjetja, kot sta Samsung Electronics in TSMC, močno vlagajo v napredne proizvodne linije, da bi zadovoljila to povpraševanje.

Še ena nova aplikacija je v avtomobilski industriji, kjer pakiranje zloženih čipov omogoča razvoj kompaktnosti, visoko zanesljivih modulov za napredne sisteme za pomoč pri vožnji (ADAS) in avtonomna vozila. Strogosti avtomobilske industrije glede upravljanja s toploto in zanesljivosti spodbujajo inovacije v tehnologijah preko-silikonskih povezav (TSV) in pakiranja na nivoju wafra, pri čemer proizvajalci, kot so Infineon Technologies in NXP Semiconductors širijo svoje portfelje za odgovarjanje na te potrebe.

Investicijska središča v letu 2025 se bodo predvidoma osredotočila okoli Azijsko-pacifiške regije, zlasti Tajvana, Južne Koreje in Kitajske, kjer vladne spodbude in robustne ekosisteme livarn pospešujejo R&D in širitev zmogljivosti. Po napovedih podjetja Gartner se pričakuje, da bo globalni trg naprednega pakiranja rasel s CAGR več kot 7 % do leta 2025, pri čemer predstavljajo rešitve zloženih čipov pomemben delež te rasti. Tveganje kapitala in strateške naložbe so prav tako usmerjene v zagonska podjetja, ki razvijajo nove materiale za povezave in tehnike heterogene integracije, kot je poudarjeno v nedavnih krogih financiranja, ki jih spremlja CB Insights.

- UI in HPC: Pakiranje zloženih čipov za pospeševalnike UI in GPU

- Avtomobilizem: Visoko zanesljivi, kompaktni moduli za ADAS in EV

- 5G/Obrobje: Rešitve z nizko zakasnitvijo in visoko širino pasu za omrežno infrastrukturo

- Azijsko-pacifiška regija: Vodilna regija za investicije in širitev proizvodnje

Na splošno bo leto 2025 videlo pakiranje mikroelektronike zloženih čipov na čelu inovacij v polprevodnikih, z močnim zagonom v področju UI, avtomobilske industrije in komunikacij, ter pomembno investicijsko dejavnostjo v Azijsko-pacifiški regiji in zagonskih podjetjih, ki se ukvarjajo z naprednimi materiali.

Izzivi, tveganja in strateške priložnosti

Pakiranje mikroelektronike zloženih čipov, temeljna komponenta napredne integracije polprevodnikov, se v letu 2025 srečuje z zapletenim obrisom izzivov in tveganj, a tudi ponuja pomembne strateške priložnosti za akterje v industriji. Glavni tehnični izziv ostaja upravljanje s toploto. Ker se čipi zlagajo vertikalno, postaja disipacija toplote vedno bolj problematična, kar ogroža zanesljivost naprav in poslabšano zmogljivost. Napredni toplotni vmesni materiali in inovativne zasnove toplotnih razpršilnikov se raziskujejo, vendar njihova integracija povečuje stroške in kompleksnost proizvodnega postopka (SEMI).

Tveganja proizvodnih in zanesljivostnih kazalcev so prav tako povečana v arhitekturah zloženih čipov. Povečano število povezav, kot so preko-silikonske povezave (TSV), povečuje verjetnost napak, kar vpliva na skupni donos. Poleg tega heterogena integracija – kombiniranje čipov z različnih procesnih vozlišč ali livarn – uvaja izzive združljivosti in testiranja. Potreba po naprednih orodjih za inšpekcijo in merjenje narašča, vendar te rešitve lahko pomembno povečajo kapitalizacijo (TechInsights).

Zapletenost dobavne verige je še en ključen rizik. Pakiranje zloženih čipov pogosto zahteva sodelovanje številnih dobaviteljev za wafre, podlage in storitve sestave. Motnje v katerem koli segmentu lahko povzročijo zamude pri proizvodnji in povečajo stroške. Geopolitikona napetost in kontrola izvoza, še posebej v trgovini s tehnologijo ZDA in Kitajske, še dodatno otežujejo ranljivosti dobavne verige (Gartner).

Kljub tem izzivom so strateške priložnosti obsežne. Povečano povpraševanje po superračunalništvu, pospeševalcih UI in naprednih mobilnih napravah spodbuja hitro sprejetje rešitev zloženih čipov. Podjetja, ki vlagajo v lastniško upravljanje s toploto, napredno testiranje in robusne strategije dobavne verige, se lahko razlikujejo in ujamejo premium сегмент trga. Poleg tega partnerstva med livarnami, OSAT (outsourced semiconductor assembly and test) in dobavitelji EDA (Electronic Design Automation) omogočajo nove zasnove in proizvodne paradigme, kot so arhitekture na osnovi čipov, ki lahko dodatno odprejo vrednost (TSMC).

- Upravljanje s toploto in zanesljivost ostajata vrh unskih tehničnih izzivov.

- Izguba dobička in stroški inšpekcije naraščajo z večjo kompleksnostjo integracije.

- Tveganja dobavne verige se povečujejo zaradi geopolitk in logističnih dejavnikov.

- Strateške naložbe v R&D, partnerstva in odpornost dobavne verige ponujajo konkurenčne prednosti.

Viri in reference

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights