2025 Rapport om marknaden för staplade die-mikroelektronikpaket: Tillväxt, teknologiska skift och strategiska insikter för de kommande 5 åren. Utforska nyckeltrender, prognoser och konkurrensdynamik som formar branschen.

- Sammanfattning & Marknadsöversikt

- Nyckelteknologitrender inom staplade die-mikroelektronikpaket

- Konkurrenslandskap och ledande aktörer

- Marknadstillväxtprognoser (2025–2030): CAGR, intäkts- och volymanalys

- Regional marknadsanalys: Nordamerika, Europa, Asien-Stillahavsområdet och resten av världen

- Framtidsutsikter: Framväxande tillämpningar och investeringshotspots

- Utmaningar, risker och strategiska möjligheter

- Källor & Referenser

Sammanfattning & Marknadsöversikt

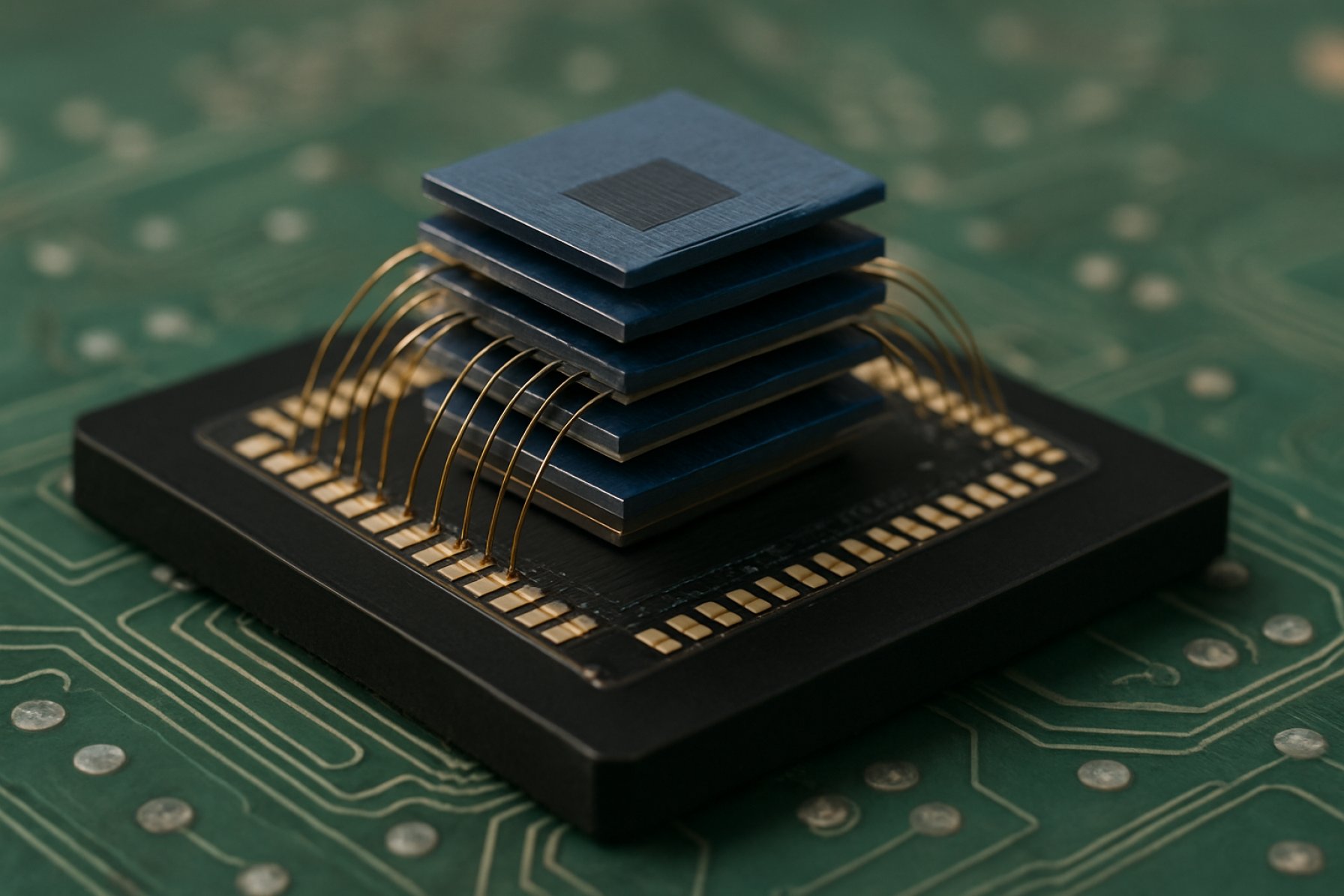

Staplade die-mikroelektronikpaket hänvisar till integrationen av flera halvledardies inom ett enda paket, arrangerade vertikalt för att optimera utrymme, prestanda och funktionalitet. Denna avancerade förpackningsteknik är avgörande för att möta de ökande kraven på miniaturisering, högre prestanda och energieffektivitet i sektorer som konsumentelektronik, automotive, telekommunikation och datacenter. Från och med 2025 upplever den globala marknaden för staplade die-mikroelektronikpaket robust tillväxt, drivet av spridningen av 5G-enheter, artificiell intelligens (AI) tillämpningar och Internet of Things (IoT).

Enligt Gartner förväntas marknaden för staplade die-paket nå en årlig tillväxttakt (CAGR) på över 8% mellan 2023 och 2027, med intäkter som förväntas överstiga 12 miljarder dollar vid 2025. Denna tillväxt stöds av den ökande användningen av 3D-integrerade kretsar (3D IC), system-in-package (SiP) lösningar och hög bandbreddminnen (HBM) moduler, som alla utnyttjar staplade die-arkitekturer för att leverera förbättrad prestanda och minskade formfaktorer.

Nyckelaktörer inom branschen, såsom TSMC, Samsung Electronics och Intel Corporation, investerar kraftigt i forskning och utveckling för att främja via-genom-silikon (TSV) och wafer-nivåpaketering (WLP) teknologier. Dessa innovationer möjliggör högre interconnect-densiteter, förbättrad termisk hantering och lägre energiförbrukning, vilket är avgörande för nästa generations tillämpningar inom AI-acceleratorer, avancerade förarassistanssystem (ADAS) och högpresterande datorer (HPC).

Regionalt dominerar Asien-Stillahavsområdet marknaden för staplade die-paket, som står för mer än 60% av den globala produktionskapaciteten, främst på grund av närvaron av ledande gjuterier och OSAT (outsourcad halvledarmontering och test) leverantörer i länder som Taiwan, Sydkorea och Kina. Nordamerika och Europa upplever också ökad adoption, särskilt inom automotive-elektronik och datacenterinfrastruktur, som noterat av IC Insights.

Sammanfattningsvis är staplade die-mikroelektronikpaket en hörnstensteknologi för halvledarindustriens utveckling i 2025, vilket möjliggör högre integration, prestanda och effektivitet över ett brett spektrum av tillämpningar. Marknadens bana formas av pågående teknologiska framsteg, strategiska investeringar från ledande aktörer och den oförtröttliga efterfrågan på smartare, mindre och mer kraftfulla elektroniska system.

Nyckelteknologitrender inom staplade die-mikroelektronikpaket

Staplade die-mikroelektronikpaket är i framkant av halvledarinnovation, vilket möjliggör högre enhetsprestanda, ökad funktionalitet och reducerade formfaktorer genom att vertikalt integrera flera halvledardies inom ett enda paket. När branschen går in i 2025 formar flera nyckelteknologitrender evolutionen och adoptionen av staplade die-paketlösningar.

- Avancerad via-genom-silikon (TSV) integration: TSV-teknologi förblir en grundsten för högdensitet die-stapling, som erbjuder låg latens och hög bandbreddsinterkonnektioner mellan vertikalt justerade dies. År 2025 förfinar tillverkarna TSV-processerna för att minska via-diameter och pitch, och därigenom öka interconnect-densiteten och förbättra elektrisk prestanda. Detta är särskilt kritiskt för högpresterande datorer (HPC) och tillämpningar inom artificiell intelligens (AI), där minnesbandbredd är en flaskhals. TSMC och Samsung Electronics leder arbetet med att kommersialisera avancerad TSV-baserad 2.5D och 3D IC-paketering.

- Hybrid bonding-tekniker: Hybrid bonding, som kombinerar direkt koppar-till-koppar och dielektrisk-till-dielectrisk bonding, får fart som en metod för att uppnå ultra-fina pitch-anslutningar och förbättrade elektriska egenskaper. Denna teknologi möjliggör stapling med under 10 mikron pitch, vilket är nödvändigt för nästa generations logik-minnesintegration. Amkor Technology och Intel Corporation har tillkännagett betydande investeringar i hybrid bonding för både minnes- och logikenheter.

- Heterogen integration: Trenden mot att integrera mångsidiga chiplets—såsom logik, minne, RF och analog—inom ett enda staplat paket accelererar. Detta tillvägagångssätt möjliggör optimerade processtyren för varje funktion, vilket förbättrar den övergripande systemprestandan och energieffektiviteten. SEMI-branschföreningen framhäver heterogen integration som en viktig möjliggörare för avancerade automotive, 5G och edge computing-lösningar.

- Innovationer inom termisk hantering: Eftersom die-stapling ökar effektens täthet utvecklas avancerade termiska gränssnittsmaterial (TIM), mikrofluidisk kylning och integrerade värmespridare för att hantera värmeavledning. Yole Group rapporterar att effektiv termisk hantering nu är en primär differentierare i design av staplade die-paket, särskilt för datacenter och AI-acceleratormarknader.

- Automatiserade tester och inspektion: Komplexiteten hos staplade die-montage kräver avancerade test- och inspektionslösningar, inklusive högupplösta röntgen och AI-drivna felupptäckter. KLA Corporation och Teradyne expanderar sina erbjudanden för att hantera de unika utmaningarna med tillförlitlighet och utbyte av flerdiepaket.

Dessa teknologitrender driver tillsammans marknaden för staplade die-mikroelektronikpaket mot högre integration, prestanda och tillförlitlighet, vilket positionerar det som en kritisk möjliggörare för nästa generations elektroniska system 2025 och framåt.

Konkurrenslandskap och ledande aktörer

Konkurrenslandskapet för marknaden för staplade die-mikroelektronikpaket 2025 karaktäriseras av intensiv innovation, strategiska partnerskap och fokus på avancerade tillverkningskapaciteter. Denna sektor drivs av efterfrågan på högre enhetsprestanda, miniaturisering och integration inom tillämpningar som smartphones, högpresterande datorer, automotive-elektronik och IoT-enheter. Nyckelaktörer utnyttjar sin expertis inom wafer-nivåpaketering, via-genom-silikon (TSV) teknologi och heterogen integration för att behålla en konkurrensfördel.

I spetsen för marknaden finns etablerade tjänsteleverantörer inom halvledarpackning och montering, inklusive Amkor Technology, ASE Technology Holding, och TSMC. Dessa företag har gjort betydande investeringar i F&U och produktionskapacitet för att stödja högvolymstillverkning av staplade die-lösningar. Till exempel, TSMC:s avancerade CoWoS (Chip-on-Wafer-on-Substrate) och SoIC (System on Integrated Chips) teknologier används allmänt för högpresterande dator- och AI-applikationer, medan Amkor Technology och ASE Technology Holding erbjuder en bred portfölj av 2.5D och 3D-paketeringstjänster för konsument- och företagsmarknader.

IDM:er (Integrated Device Manufacturers) som Intel Corporation och Samsung Electronics är också framträdande, där de integrerar staplade die-paket i sina produktplaner för att förbättra chip-prestanda och energieffektivitet. Intels Foveros-teknik och Samsungs X-Cube-plattform exemplifierar proprietära tillvägagångssätt för vertikal integration och chiplet-baserade arkitekturer.

Nytillkomna spelare och nischspecialister, inklusive JCET Group och Powertech Technology Inc., vinner mark genom att erbjuda skräddarsydda lösningar och rikta in sig på specifika vertikaler som automotive och industriell elektronik. Dessa företag samarbetar ofta med fabless halvledarföretag och systemintegratörer för att leverera skräddarsydda staplade die-paket.

Den konkurrensutsatta miljön formas ytterligare av pågående M&A-aktivitet, teknologilicensering och joint ventures, då företag strävar efter att utvidga sina kapabiliteter och globala räckvidd. Enligt Yole Group förväntas marknaden se en fortsatt konsolidering, med ledande aktörer som investerar i nästa generations interkonnektioner, avancerade material och automatisering för att möta de föränderliga behoven inom AI, 5G och edge computing-marknader.

Marknadstillväxtprognoser (2025–2030): CAGR, intäkts- och volymanalys

Marknaden för staplade die-mikroelektronikpaket är redo för robust tillväxt mellan 2025 och 2030, drivet av den ökande efterfrågan på högpresterande, miniaturiserade elektroniska enheter inom konsumentelektronik, automotive, och datacenterapplikationer. Enligt prognoser från MarketsandMarkets förväntas den globala marknaden för 3D IC och staplade die-paketering registrera en årlig tillväxttakt (CAGR) på ungefär 12% under denna period. Denna tillväxtbana stöds av den ökande användningen av avancerade paketeringslösningar för att adressera begränsningarna hos traditionella 2D-arkitekturer, särskilt när det gäller energieffektivitet, formfaktor och bandbredd.

Intäktsprognoser indikerar att segmentet för staplade die-mikroelektronikpaket kommer att överstiga USD 15 miljarder till 2030, upp från ett uppskattat USD 8,5 miljarder 2025. Denna ökning tillskrivs spridningen av artificiell intelligens (AI), 5G-infrastruktur och edge computing, som alla kräver högre interconnect-densitet och förbättrad termisk hantering—nyckelfördelar som erbjuds av staplade die-arkitekturer. Gartner framhäver att halvledarindustrins skifte mot heterogen integration och system-in-paket (SiP) lösningar ytterligare kommer att påskynda adoptionen av staplade die-paketeringsteknologier.

Vad gäller volym förväntas antalet skickade staplade die-enheter växa med en CAGR på 13–14% från 2025 till 2030, vilket återspeglar både ökad penetration inom högvolymskonsumentenheter och utvidgad användning inom automotive-elektronik och industriell IoT. Yole Group rapporterar att ledande gjuterier och OSAT:s (outsourcad halvledarmontering och testleverantörer) ökar sina investeringar i avancerade paketeringslinjer för att möta denna förväntade efterfrågan, där Asien-Stillahavsområdet förblir det dominerande produktionsnavet på grund av sitt etablerade halvledartillverkningssystem.

- CAGR (2025–2030): 12–14%

- Intäkter (2030): USD 15+ miljarder

- Volymtillväxt: Drivs av konsumentelektronik, automotive, och datacenterapplikationer

- Nyckelregioner: Asien-Stillahavsområdet leder, följt av Nordamerika och Europa

Övergripande sett är marknaden för staplade die-mikroelektronikpaket inställd på betydande expansion, drivet av teknologisk innovation och den oförtröttliga strävan efter högre prestanda och integration i nästa generations elektroniska system.

Regional marknadsanalys: Nordamerika, Europa, Asien-Stillahavsområdet och resten av världen

Den globala marknaden för staplade die-mikroelektronikpaket upplever dynamisk tillväxt, med regionala trender som formas av teknologisk innovation, slutanvändarefterfrågan och utvecklingen inom försörjningskedjan. År 2025 presenterar Nordamerika, Europa, Asien-Stillahavsområdet och resten av världen (RoW) tydliga marknadskarakteristika och tillväxtdrivare.

- Nordamerika: Den nordamerikanska marknaden drivs av robusta investeringar i avancerad halvledartillverkning och en stark närvaro av ledande teknikföretag. Regionen gynnas av betydande F&U-aktiviteter, särskilt i USA, där strävan efter inhemsk chipproduktion stöds av regeringsinitiativ som CHIPS Act. Nyckeltillämpningar inkluderar högpresterande datorer, automotive-elektronik och försvarssystem. Enligt Semiconductor Industry Association förväntas Nordamerika upprätthålla stabil tillväxt inom staplade die-paketering, driven av efterfrågan på miniaturiserade, högdensitetslösningar inom AI och 5G-infrastruktur.

- Europa: Europas marknad kännetecknas av fokus på automotive, industriell automation och IoT-applikationer. Regionens betoning på kvalitet och tillförlitlighet, tillsammans med strikta regulatoriska standarder, främjar adoptionen av avancerade paketeringsteknologier. Initiativ som European Chips Act har som mål att stärka lokala halvledarkapabiliteter. Enligt SEMI investerar europeiska tillverkare i allt större utsträckning i staplade die-lösningar för att stödja regionens växande elfordons- och smarta tillverkningssektorer.

- Asien-Stillahavsområdet: Asien-Stillahavsområdet dominerar den globala marknaden för staplade die-mikroelektronikpaket, med störst andel 2025. Denna ledarskap stöds av närvaron av stora gjuterier och OSAT (outsourcad halvledarmontering och test) leverantörer i länder som Taiwan, Sydkorea, Kina och Japan. Regionens snabba adoption av konsumentelektronik, smartphones och datacenter driver efterfrågan på högdensitetspaketering. Enligt IC Insights accelereras Asien-Stillahavsområdets marknadstillväxt ytterligare av statliga incitament och aggressiva kapacitetsutvidgningar av ledande aktörer.

- Resten av världen (RoW): RoW-segmentet, inklusive Latinamerika, Mellanöstern och Afrika, förblir tidigt men visar potential för tillväxt när digitala transformationsinitiativ expanderar. Investeringar i telekommunikationsinfrastruktur och framväxande elektroniktillverkningsnav förväntas gradvis öka efterfrågan på staplade die-paketeringslösningar, som noterats av Gartner.

Övergripande reflekterar de regionala dynamikerna 2025 en samsyn av innovation, politiskt stöd och efterfrågan på slutmarknaden, där Asien-Stillahavsområdet leder i volym och Nordamerika och Europa fokuserar på högvärdiga, specialiserade tillämpningar.

Framtidsutsikter: Framväxande tillämpningar och investeringshotspots

Framtidsutsikterna för staplade die-mikroelektronikpaket 2025 formas av snabba framsteg inom halvledarintegration, spridningen av AI och högpresterande datorer, samt den växande efterfrågan på miniaturiserade, högdensitets elektroniska system. Staplade die-paketering, som involverar vertikal integration av flera halvledardies inom ett enda paket, erkänns alltmer som en nyckelmöjliggörare för nästa generations enheter inom flera högväxande sektorer.

Framväxande tillämpningar är särskilt framträdande inom datacenter, 5G-infrastruktur och edge computing. Behovet av högre bandbredd och lägre latens i dessa miljöer driver adoptionen av 2.5D och 3D-staplade die-arkitekturer, som erbjuder förbättrad elektrisk prestanda och minskade anslutningslängder. År 2025 förväntas integrationen av högbandwidthminnen (HBM) med logikdies accelerera, vilket stödjer de beräkningsmässiga kraven för AI-acceleratorer och avancerade grafikprocessorer. Företag som Samsung Electronics och TSMC investerar kraftigt i avancerade paketeringslinjer för att möta denna efterfrågan.

En annan framväxande tillämpning är inom automotive-sektorn, där staplade die-paketering möjliggör utvecklingen av kompakta, högtillförlitliga moduler för avancerade förarassistanssystem (ADAS) och autonoma fordon. Automotive-industriens stränga krav på termisk hantering och tillförlitlighet driver innovation inom via-genom-silikon (TSV) och wafer-nivåpaketeringsteknologier, med leverantörer som Infineon Technologies och NXP Semiconductors som expanderar sina portföljer för att möta dessa behov.

Investeringshotspots 2025 förväntas centrera kring Asien-Stillahavsområdet, särskilt Taiwan, Sydkorea och Kina, där statliga incitament och robusta gjuteri-ekosystem accelererar F&U och kapacitetsutvidgning. Enligt Gartner förväntas den globala marknaden för avancerad paketering växa med en CAGR på över 7% fram till 2025, där staplade die-lösningar representerar en betydande del av denna tillväxt. Riskkapital och strategiska investeringar flödar också in i startups som utvecklar nya interconnect-material och tekniker för heterogen integration, som framhävts av nyligen spårade finansieringsrundor av CB Insights.

- AI och HPC: Staplade die-paketering för AI-acceleratorer och GPU:er

- Automotive: Hårtillförlitliga, kompakta moduler för ADAS och EV:er

- 5G/Edge: Låg latens, hög bandbredslösningar för nätverksinfrastruktur

- Asien-Stillahavsområdet: Ledande region för investeringar och tillverkningsutvidgning

Sammanfattningsvis kommer 2025 se staplade die-mikroelektronikpaket i framkant av halvledarinnovation, med stark momentum inom AI, automotive och kommunikation, och betydande investeringsaktivitet inom Asien-Stillahavsområdet och startups för avancerade material.

Utmaningar, risker och strategiska möjligheter

Staplade die-mikroelektronikpaket, en hörnsten för avancerad halvledarintegration, står inför ett komplext landskap av utmaningar och risker år 2025, men presenterar också betydande strategiska möjligheter för branschaktörer. Den främsta tekniska utmaningen förblir termisk hantering. Eftersom fler dies är vertikalt integrerade blir värmeavledning allt mer problematisk, vilket riskerar enhetens tillförlitlighet och prestandaförsämring. Avancerade termiska gränssnittsmaterial och innovativa värmespridarutformningar utforskas, men deras integration ökar kostnader och komplexitet i tillverkningsprocessen (SEMI).

Avkastning och tillförlitlighetsrisker är också högre i staplade die-arkitekturer. Det ökade antalet anslutningar, såsom via-genom-silikon (TSV), ökar sannolikheten för defekter, vilket påverkar den totala uppnående. Dessutom introducerar heterogen integration—kombinera dies från olika processnoder eller gjuterier—kompatibilitets- och testutmaningar. Behovet av avancerade inspektions- och mätverktyg ökar, men dessa lösningar kan kraftigt öka kapitalkostnaderna (TechInsights).

Leveranskedjans komplexitet är en annan kritisk risk. Staplade die-paketering kräver ofta samarbete över flera leverantörer för wafer, substrat och monteringtjänster. Störningar i vilket segment som helst kan fördröja produktionen och öka kostnader. Geopolitiska spänningar och exportkontroller, särskilt inom den amerikansk-kinesiska teknikhandeln, förvärrar ytterligare sårbarheterna i försörjningskedjan (Gartner).

Trots dessa utmaningar finns det strategiska möjligheter. Efterfrågan på högpresterande datorer, AI-acceleratorer och avancerade mobila enheter driver snabb adoption av staplade die-lösningar. Företag som investerar i proprietär termisk hantering, avancerad testning och robusta strategier för försörjningskedjan kan differentiera sig och fånga premium marknadssegment. Dessutom möjliggör partnerskap mellan gjuterier, OSAT:s (outsourcad halvledarmontering och test) och EDA (Electronic Design Automation) leverantörer nya design- och tillverkningsparadigmer, såsom chiplet-baserade arkitekturer, vilket ytterligare kan frigöra värde (TSMC).

- Termisk hantering och tillförlitlighet förblir de främsta tekniska hindren.

- Avkastning och inspektionskostnader ökar med den ökade integrationskomplexiteten.

- Risker i leveranskedjan förvärras av geopolitiska och logistiska faktorer.

- Strategiska investeringar i FoU, partnerskap och motståndskraft i leveranskedjan erbjuder konkurrensfördelar.

Källor & Referenser

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Semiconductor Industry Association

- Infineon Technologies

- NXP Semiconductors

- TechInsights