Звіт ринку пакування мікроелектроніки з укладеними чіпами 2025 року: Зростання, технологічні зміни та стратегічні інсайти на найближчі 5 років. Досліджте ключові тенденції, прогнози та конкурентну динаміку, що формують індустрію.

- Резюме та огляд ринку

- Основні технологічні тенденції в пакуванні мікроелектроніки з укладеними чіпами

- Конкурентне середовище та провідні гравці

- Прогнози зростання ринку (2025–2030): CAGR, аналіз доходів і обсягу

- Регіональний аналіз ринку: Північна Америка, Європа, Азіатсько-Тихоокеанський регіон та інші регіони

- Перспективи майбутнього: нові застосування та інвестиційні гарячі точки

- Виклики, ризики та стратегічні можливості

- Джерела та посилання

Резюме та огляд ринку

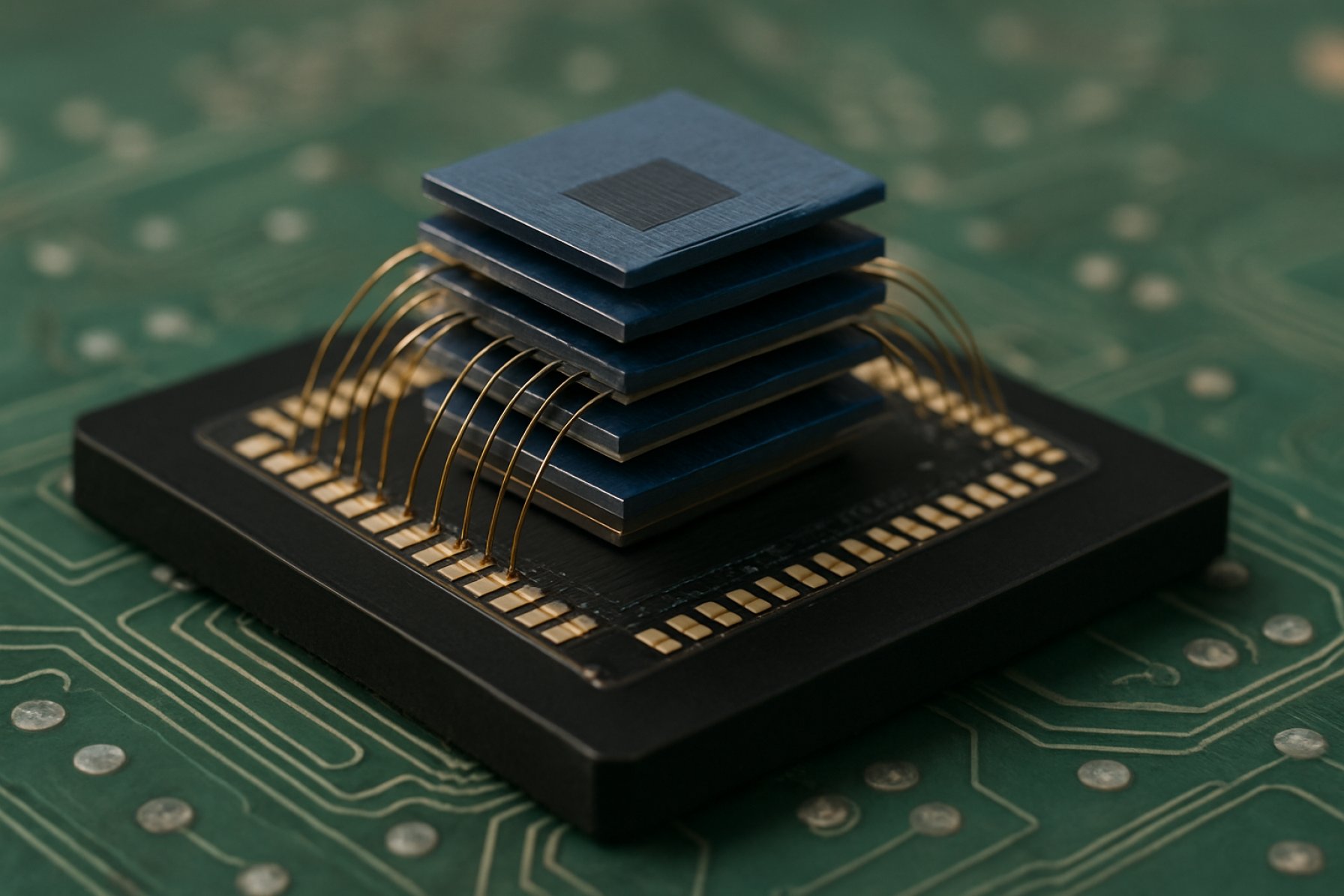

Пакування мікроелектроніки з укладеними чіпами передбачає інтеграцію кількох напівпровідникових чіпів в одному пакеті, розташованих вертикально для оптимізації простору, продуктивності та функціональності. Ця технологія просунутого пакування є ключовою для виконання зростаючих вимог до мініатюризації, вищої продуктивності та енергоефективності в секторах, таких як споживча електроніка, автомобільна промисловість, телекомунікації та центри обробки даних. Станом на 2025 рік, світовий ринок пакування мікроелектроніки з укладеними чіпами демонструє стійке зростання під впливом поширення 5G пристроїв, застосувань штучного інтелекту (ШІ) та Інтернету речей (IoT).

Згідно з Gartner, ринок пакування з укладеними чіпами прогнозується на досягнення середньорічного темпу зростання (CAGR) понад 8% у період з 2023 по 2027 рік, при цьому доходи, як очікується, перевищать 12 мільярдів доларів до 2025 року. Це зростання підтримується зростаючим впровадженням 3D інтегральних схем (3D IC), рішень системи в пакет (SiP) та модулів пам’яті з високою пропускною здатністю (HBM), які всі використовують архітектури укладених чіпів для забезпечення підвищеної продуктивності та зменшених розмірів.

Ключові гравці галузі, такі як TSMC, Samsung Electronics та Intel Corporation, значно інвестують у наукові дослідження та розробки, щоб просунути технології вертикальних з’єднань (TSV) та пакування на рівні пластин (WLP). Ці інновації дозволяють досягти вищої щільності з’єднань, покращеного теплового управління та зниження споживання енергії, що є критично важливим для наступного покоління застосувань у прискорювачах ШІ, прогресивних системах допомоги водієві (ADAS) та високопродуктивних обчисленнях (HPC).

Регіонально, Азіатсько-Тихоокеанський регіон домінує на ринку пакування з укладеними чіпами, займаючи більше 60% світової виробничої потужності, здебільшого через присутність провідних фабрик та постачальників послуг OSAT (зовнішня збірка та тестування напівпровідників) у країнах, таких як Тайвань, Південна Корея та Китай. Північна Америка та Європа також спостерігають збільшення впровадження, особливо у електроніці автомобілів та інфраструктурі центрів обробки даних, як зазначає IC Insights.

Таким чином, пакування мікроелектроніки з укладеними чіпами є основною технологією еволюції напівпровідникової індустрії в 2025 році, що дозволяє досягати вищого рівня інтеграції, продуктивності та ефективності в широкому спектрі застосувань. Траєкторія ринку формується завдяки постійним технологічним досягненням, стратегічним інвестиціям провідних гравців та невпинному попиту на більш розумні, менші та потужніші електронні системи.

Основні технологічні тенденції в пакуванні мікроелектроніки з укладеними чіпами

Пакування мікроелектроніки з укладеними чіпами знаходиться на передовій інновацій у сфері напівпровідників, що дозволяє досягати високої продуктивності пристроїв, підвищеної функціональності та зменшених розмірів завдяки вертикальній інтеграції кількох напівпровідникових чіпів в одному пакеті. Як індустрія переходить у 2025 рік, кілька основних технологічних тенденцій формують еволюцію та впровадження рішень пакування з укладеними чіпами.

- Розвинена інтеграція через-силіконовими з’єднаннями (TSV): Технологія TSV залишається основною для укладки чіпів з високою щільністю, пропонуючи з’єднання з низькою затримкою та високою пропускною здатністю між вертикально вирівняними чіпами. У 2025 році виробники вдосконалюють процеси TSV, щоб зменшити діаметр і відстань між з’єднаннями, таким чином підвищуючи щільність з’єднань і покращуючи електричні характеристики. Це особливо критично для високопродуктивних обчислень (HPC) та застосувань штучного інтелекту (ШІ), де пропускна здатність пам’яті є вузьким місцем. TSMC та Samsung Electronics є лідерами на ринку комерціалізації передового пакування на основі TSV з 2.5D та 3D IC.

- Гібридні методи з’єднання: Гібридне з’єднання, яке поєднує пряме з’єднання мідь до міді та діелектричне з’єднання до діелектричного, набуває популярності як метод для досягнення ультра-малих відстаней між з’єднаннями та покращення електричних характеристик. Ця технологія дозволяє укладати з відстанню менше 10 мікрон, що є суттєвим для інтеграції логіки та пам’яті нового покоління. Amkor Technology та Intel Corporation оголосили про значні інвестиції в гібридне з’єднання для пам’яті та логічних пристроїв.

- Гетерогенна інтеграція: Тенденція до інтеграції різноманітних чіпів — таких як логіка, пам’ять, RF та аналогові — в одному укладеному пакеті прискорюється. Цей підхід дозволяє оптимізувати процеси для кожної функції, покращуючи загальну продуктивність системи та енергетичну ефективність. Галузева асоціація SEMI підкреслює гетерогенну інтеграцію як ключовий фактор для розвинених автомобільних, 5G та рішень для краю.

- Інновації в термічному управлінні: У міру збільшення щільності потужності в укладених чіпах розробляються передові термічні інтерфейсні матеріали (TIM), мікрофлюїдне охолодження та інтегровані розподільники тепла для управління відведенням тепла. Yole Group повідомляє, що ефективне термічне управління зараз є основною відмінною рисою дизайну укладених чіпів, особливо для ринків центрів обробки даних та прискорювачів ШІ.

- Автоматизоване тестування та інспекція: Складність складання укладених чіпів вимагає розробки передових рішень для тестування та інспекції, включаючи рентгенівське зображення високої роздільної здатності та визначення дефектів на основі ШІ. KLA Corporation та Teradyne розширюють свої пропозиції, щоб вирішувати унікальні проблеми надійності та врожайності пакетів з кількома чіпами.

Ці технологічні тенденції колективно сприяють руху ринку пакування мікроелектроніки з укладеними чіпами до більшої інтеграції, продуктивності та надійності, позиціонуючи його як критичного фактора для наступного покоління електронних систем у 2025 році та далі.

Конкурентне середовище та провідні гравці

Конкурентне середовище ринку пакування мікроелектроніки з укладеними чіпами у 2025 році характеризується інтенсивною інновацією, стратегічними партнерствами та акцентом на сучасних виробничих потужностях. Цей сектор підживлюється попитом на вищу продуктивність пристроїв, мініатюризацію та інтеграцію в таких застосуваннях, як смартфони, високопродуктивні обчислення, електроніка в автомобілях та пристрої IoT. Ключові гравці використовують свій досвід у пакуванні на рівні пластин, технології через-силіконових з’єднань (TSV) та гетерогенної інтеграції, щоб зберегти конкурентоспроможність.

На ринку ведуть позиції усталені постачальники послуг пакування та збору напівпровідників, такі як Amkor Technology, ASE Technology Holding та TSMC. Ці компанії зробили значні інвестиції в R&D та виробничі потужності, щоб підтримати масове виробництво рішень з укладеними чіпами. Наприклад, передові технології TSMC, такі як CoWoS (Chip-on-Wafer-on-Substrate) і SoIC (System on Integrated Chips), широко використовуються для висококласних обчислень та застосувань ШІ, тоді як Amkor Technology і ASE Technology Holding пропонують широкий спектр послуг пакування 2.5D і 3D для споживчих та корпоративних ринків.

IDM (вбудовані виробники пристроїв) такі як Intel Corporation та Samsung Electronics також займають помітне місце, інтегруючи пакування з укладеними чіпами у свої продуктові плани для підвищення продуктивності чіпів та енергетичної ефективності. Технології Foveros від Intel та платформа X-Cube від Samsung демонструють унікальні підходи до вертикальної інтеграції та архітектур на базі чіплетів.

Нові компанії та нішеві спецалісти, такі як JCET Group та Powertech Technology Inc., набирають популярність, пропонуючи індивідуальні рішення та націлюючись на певні вертикалі, такі як автомобільна та промислова електроніка. Ці компанії часто співпрацюють з fabs (безфабричні напівпровідникові компанії) та системними інтеграторами, щоб доставляти адаптовані пакети з укладеними чіпами.

Конкурентне середовище також визначається поточними активностями злиттів та поглинань, ліцензування технологій та спільних підприємств, оскільки компанії намагаються розширити свої можливості та глобальне охоплення. Згідно з Yole Group, ринок очікує подальше консолідацію, при цьому провідні гравці інвестують у наступні покоління з’єднань, передові матеріали та автоматизацію, щоб відповідати еволюційним потребам ринків ШІ, 5G та обробки даних на краю.

Прогнози зростання ринку (2025–2030): CAGR, аналіз доходів і обсягу

Ринок пакування мікроелектроніки з укладеними чіпами готовий до рішучого зростання в період з 2025 по 2030 рік, підживлюваного зростаючим попитом на високопродуктивні, мініатюризовані електронні пристрої в секторах споживчої електроніки, автомобільної промисловості та центрів обробки даних. Згідно з прогнозами MarketsandMarkets, глобальний ринок 3D IC та пакування з укладеними чіпами очікується з реєстрацією середньорічного темпу зростання (CAGR) приблизно 12% протягом цього періоду. Ця траєкторія зростання ґрунтується на збільшенні впровадження передових пакувальних рішень для усунення обмежень традиційних 2D архітектур, особливо з точки зору енергоефективності, форм-фактора та пропускної здатності.

Прогнози доходів свідчать, що сегмент пакування мікроелектроніки з укладеними чіпами перевищить 15 мільярдів доларів США до 2030 року, збільшившись з приблизно 8.5 мільярдів доларів США у 2025 році. Це зростання викликане поширенням штучного інтелекту (ШІ), інфраструктури 5G та обробки даних на краю, які всі потребують вищої щільності з’єднання та покращеного термічного управління – ключових переваг, які пропонують архітектури з укладеними чіпами. Gartner підкреслює, що зсув напівпровідникової індустрії до гетерогенної інтеграції та рішень системи в пакеті (SiP) ще більше прискорить впровадження технологій пакування з укладеними чіпами.

Щодо обсягу, кількість одиниць укладених чіпів, що відвантажуються, прогнозується з ростом CAGR 13–14% з 2025 по 2030 рік, що відображає як збільшення проникнення у високобюджетні споживчі пристрої, так і розширене використання в автомобільній електроніці та промисловому IoT. Yole Group повідомляє, що провідні фабрики та OSAT (зовнішні постачальники послуг збору та тестування напівпровідників) нарощують інвестиції в лінії передового пакування, щоб задовольнити цей очікуваний попит, при цьому Азіатсько-Тихоокеанський регіон залишається домінуючим виробничим центром через свою усталену екосистему виробництва напівпровідників.

- CAGR (2025–2030): 12–14%

- Доходи (2030): USD 15+ мільярдів

- Зростання обсягів: Підтримується споживчою електронікою, автомобільною і центрами обробки даних

- Ключові регіони: Азіатсько-Тихоокеанський регіон лідирує, за ним слідують Північна Америка та Європа

Отже, ринок пакування мікроелектроніки з укладеними чіпами готується до значного розширення, що підживлюється технологічною інновацією та невпинним прагненням до вищої продуктивності та інтеграції в електронних системах наступного покоління.

Регіональний аналіз ринку: Північна Америка, Європа, Азіатсько-Тихоокеанський регіон та інші регіони

Світовий ринок пакування мікроелектроніки з укладеними чіпами демонструє динамічне зростання, при цьому регіональні тенденції формуються під впливом технологічних нововведень, попиту кінцевих споживачів та розробки ланцюгів постачання. У 2025 році ринки Північної Америки, Європи, Азіатсько-Тихоокеанського регіону та інших регіонів демонструють унікальні ринкові характеристики та рушійні сили зростання.

- Північна Америка: Ринок Північної Америки підтримується значними інвестиціями в передове виробництво напівпровідників та сильною присутністю провідних технологічних компаній. Регион отримує вигоди від значних наукових досліджень, особливо в США, де прагнення до вітчизняного виробництва чипів підтримується державними ініціативами, такими як Закон про чипи. Ключові застосування включають високопродуктивні обчислення, електроніку в автомобілях та системи оборони. Згідно з Асоціацією індустрії напівпровідників, Північна Америка, ймовірно, збережеться з постійним зростанням в пакуванні з укладеними чіпами, підживлюваним попитом на мініатюризовані, високощільні рішення в AI та 5G інфраструктурах.

- Європа: Ринок Європи характеризується акцентом на автомобільній промисловості, промисловій автоматизації та IoT-додатках. Акцент регіону на якості та надійності, а також суворі регуляторні стандарти сприяють впровадженню передових технологій пакування. Ініціативи, такі як Європейський закон про чипи, спрямовані на зміцнення місцевих спроможностей у сфері напівпровідників. Згідно з SEMI, європейські виробники все частіше інвестують у рішення з укладеними чіпами для підтримки зростаючих секторів електричних автомобілів та розумного виробництва.

- Азіатсько-Тихоокеанський регіон: Азіатсько-Тихоокеанський регіон домінує на світовому ринку пакування мікроелектроніки з укладеними чіпами, займаючи найбільшу частку в 2025 році. Це лідерство підкріплюється наявністю великих фабрик та OSAT (зовнішні постачальники послуг збору та тестування напівпровідників) у країнах, таких як Тайвань, Південна Корея, Китай та Японія. Швидка адаптація споживчої електроніки, смартфонів та центрів обробки даних стимулює попит на пакування з високою щільністю. Згідно з IC Insights, зростання ринку Азіатсько-Тихоокеанського регіону також прискорюється завдяки державним стимулам та агресивним розширенням потужностей провідних гравців.

- Інші регіони: Сегмент інших регіонів, включаючи Латинську Америку, Близький Схід та Африку, залишається недорозвиненим, але демонструє потенціал для зростання у міру розвитку ініціатив цифрової трансформації. Інвестиції в інфраструктуру телекомунікацій та нові центри виробництва електроніки, як зазначає Gartner, очікують поступове зростання попиту на рішення з укладеними чіпами.

Загалом, регіональна динаміка у 2025 році відображає зближення інновацій, підтримки політики та попиту кінцевих ринків, при цьому Азіатсько-Тихоокеанський регіон лідирує за обсягами, а Північна Америка та Європа зосереджуються на високовартісних, спеціалізованих застосуваннях.

Перспективи майбутнього: нові застосування та інвестиційні гарячі точки

Перспективи для пакування мікроелектроніки з укладеними чіпами у 2025 році формуються стрімкими досягненнями в інтеграції напівпровідників, поширенням ШІ та високопродуктивних обчислень, а також зростаючим попитом на мініатюризовані, високощільні електронні системи. Пакування з укладеними чіпами, яке передбачає вертикальну інтеграцію кількох напівпровідникових чіпів в один пакет, все більше визнається як ключовий фактор для пристроїв наступного покоління в кількох секторах з високим потенціалом зростання.

Нові застосування особливо актуальні в центрах обробки даних, інфраструктурі 5G та обробці даних на краю. Потреба у вищій пропускній здатності та зниженій затримці в цих середовищах стимулює впровадження архітектур з укладеними чіпами 2.5D та 3D, які пропонують покращену електричну продуктивність та зменшену довжину з’єднань. У 2025 році інтеграція пам’яті з високою пропускною здатністю (HBM) з логічними чіпами очікується на прискорення, підтримуючи обчислювальні вимоги прискорювачів ШІ та розвинутих графічних процесорів. Компанії, такі як Samsung Electronics та TSMC, значно інвестують у сучасні лінії пакування, щоб задовольнити цей попит.

Інша нова сфера застосування полягає в автомобільному секторі, де пакування з укладеними чіпами дає змогу розробляти компактні, надійні модулі для прогресивних систем допомоги водієві (ADAS) та автономних транспортних засобів. Суворі вимоги автомобільної промисловості до термічного управління та надійності стимулюють інновації в технологіях через-силіконових з’єднань (TSV) та пакування на рівні плат, де такі постачальники, як Infineon Technologies та NXP Semiconductors, розширюють свої портфоліо для задоволення цих потреб.

Очікується, що інвестиційні гарячі точки у 2025 році зосередяться на Азіатсько-Тихоокеанському регіоні, особливо Тайвані, Південній Кореї та Китаї, де державні стимули та потужні екосистеми виробництв прискорюють R&D та розширення потужностей. Згідно з Gartner, глобальний ринок передового пакування прогнозується з CAGR понад 7% до 2025 року, при цьому рішення з укладеними чіпами становитимуть значну частку цього зростання. Венчурний капітал та стратегічні інвестиції також надходять в стартапи, які розробляють нові матеріали для з’єднань та технології гетерогенної інтеграції, на які звертає увагу кількість недавніх раундов фінансування, що відслідковуються CB Insights.

- ШІ та HPC: Пакування з укладеними чіпами для прискорювачів ШІ та GPU

- Автомобільний сектор: Високонадійні, компактні модулі для ADAS та електромобілів

- 5G/Край: Рішення з низькою затримкою та високою пропускною здатністю для мережевої інфраструктури

- Азіатсько-Тихоокеанський регіон: Лідируючий регіон для інвестицій і розширення виробництв

Таким чином, у 2025 році пакування мікроелектроніки з укладеними чіпами стоятиме на передовій інновацій у сфері напівпровідників, з сильним імпульсом в ШІ, автомобільному та комунікаційному секторах, а також значною інвестиційною активністю в Азіатсько-Тихоокеанському регіоні та стартапах в області передових матеріалів.

Виклики, ризики та стратегічні можливості

Пакування мікроелектроніки з укладеними чіпами, що є ключовим елементом просунутої інтеграції напівпровідників, стикається з комплексним ландшафтом викликів та ризиків у 2025 році, але також відкриває значні стратегічні можливості для гравців індустрії. Основним технічним викликом залишається теплове управління. Оскільки дедалі більше чіпів інтегруються вертикально, відведення тепла стає несподівано проблемним, ставлячи під загрозу надійність пристроїв та погіршуючи продуктивність. Вивчені передові термічні інтерфейсні матеріали та інноваційні дизайни розподільників тепла, але їх інтеграція підвищує витрати та ускладнює виробничий процес (SEMI).

Ризики врожайності та надійності також загострюються в архітектурах з укладеними чіпами. Збільшена кількість з’єднань, таких як через-силіконові з’єднання (TSV), підвищує ймовірність дефектів, що впливає на загальну врожайність. Крім того, гетерогенна інтеграція — поєднання чіпів з різних технологічних вузлів або фабрик — представляє виклики щодо сумісності та тестування. Потреба в сучасних інструментах для інспекції та метрології зростає, але ці рішення можуть помітно підвищити капітальні витрати (TechInsights).

Складність ланцюга постачання є ще одним критичним ризиком. Пакування з укладеними чіпами часто вимагає співпраці між кількома постачальниками, які забезпечують пластини, підкладки та послуги збору. Порушення в будь-якому сегменті можуть призвести до затримок у виробництві та підвищення витрат. Геополітичні напруження та експортні обмеження, особливо в США-Китаї, ще більше ускладнюють вразливість ланцюга постачання (Gartner).

Несмотря на ці виклики, стратегічних можливостей багато. Потреба в високопродуктивних обчисленнях, прискорювачах ШІ та удосконалених мобільних пристроях стимулює стрімке впровадження рішень з укладеними чіпами. Компанії, які інвестують у власне термічне управління, розширене тестування та надійні стратегії ланцюга постачання, можуть відрізнятись та завойовувати преміум-сегменти ринку. Крім того, партнерства між фабриками, OSAT (зовнішні постачальники послуг збору та тестування) та постачальниками EDA (автоматизація проектування електроніки) дозволяють створювати нові парадигми дизайну та виробництва, такі як архітектури на базі чіплетів, що може додатково розкрити цінність (TSMC).

- Теплове управління та надійність залишаються основними технічними перешкодами.

- Втрати врожайності та витрати на інспекцію зростають через збільшення складності інтеграції.

- Ризики ланцюга постачання посилюються геополітичними та логістичними факторами.

- Стратегічні інвестиції в R&D, партнерства та стійкість ланцюга постачання пропонують конкурентні переваги.

Джерела та посилання

- IC Insights

- Amkor Technology

- KLA Corporation

- ASE Technology Holding

- JCET Group

- Powertech Technology Inc.

- MarketsandMarkets

- Асоціація індустрії напівпровідників

- Infineon Technologies

- NXP Semiconductors

- TechInsights